Pre-Laboratory #2 ECE 2022 1 Introduction 2 Operation of a 4 bit

advertisement

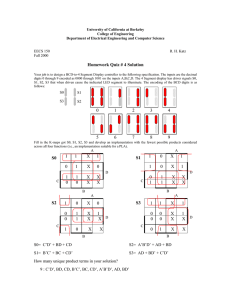

Name: ECE Box Number: Name: ECE Box Number: Pre-Laboratory #2 ECE 2022 1 Introduction The topic of lab 2 is design of combinatorial logic via basic logic simplification. In this pre-lab you will design a 2 bit BCD to 7 Segment decoder, simplify the logic, and draw the logic circuit schematic. Upon completion of this pre-lab you should have the following items completed: 1. Completed Truth Table 2. Completed Karnaugh Maps 3. Simplified logic equations 4. Decoder circuit schematic Bring the completed pre-lab to your lab session and have the teaching assistant review your circuit before you begin construction. During the laboratory session you will both build your 2 bit decoder and also construct a 4 bit BCD to 7 Segment Decoder based upon a pre-packaged decoder that can be obtained commericially as a single logic IC chip. 2 Operation of a 4 bit BCD to 7 Segment Decoder A 4 bit BCD to 7 Segment Decoder is a combinatorial logic circuit that converts a 4 bit binary code for the values 0-9 into a 7 bit binary code that determines which one or more light-segments of a 7 segment display should be illuminated to form the usual form (arabic) of the single digit decimal number. The functionality of the 2 bit BCD to 7 Segment decoder you will design will be similar to the integrated circuit 7447 decoder which is described in the Floyd text on pages 320–324. Your decoder will not have the lamp test, blanking input, and ripple blanking input signals and will only decode the numbers 0–4 for display in order to greatly reduce the complexity of the design and construction. A 4 bit BCD to 7 Segment decoder has four inputs called D0 , D1 , D2 , and D3 . Using these four input bits a number between 0 and 15 can be represented. The input D3 is called the most significant bit (MSB) and the input D0 is called the least significant bit (LSB). Therefore, D3 stands for 23 and D0 for 20 . The decoder you will design has seven outputs, one for each segment of the 7 segment display. The segments are labeled ‘a’ though ‘g’ as shown in Figure 1. The 4 bit BCD to 7 Segment decoder has to take a binary number on the input and decode it to light up the appropriate segments on the 7 segment display. Figure 1 shows the outputs that the 1 2 ECE 2022 Pre-Lab 2 a f g e b c d dp Figure 1: 7 Segment Display Labels decoder must generate. The display unit for which you will be designing a decoder in this pre-lab has a common anode. This means that a logical ‘0’ will light up a segment whereas a logical ‘1’ will switch a segment off. Figure 2: 7 Segment Display Outputs 2.1 Truth Table Your first task in designing the decoder is to complete Table 1, also called a truth table. Remember that a ‘1’ will switch off a segment and a ‘0’ will switch it on. The 2 bit BCD to 7 Segment decoder has to take a binary number on the input and decode it to light up the appropriate segments on the 7 segment display. As mentioned before, Figure 2 shows the all outputs that a full 4 bit BCD to 7 Segment decoder must generate.Since with 2 inputs you can only represent numbers 0 to 3, you will only be using the first four of these digit representation diagrams. Complete the truth table (see Table 1) for this decoder. The display unit for which you will be designing a decoder has a common anode. This means that a logical ‘0’ will light up a segment whereas a logical ‘1’ will switch a segment off. We have filled in the first line so that you check your understanding of this last point. 0 D1 D0 a b c d e f g 0 0 0 0 0 0 0 0 1 1 2 3 Table 1: 2 bit BCD to 7 Segment Decoder Truth Table 3 ECE 2022 Pre-Lab 2 2.2 Karnaugh Maps You can see directly from the truth table that you will not need a Karnough map to simplify the logic for every segment. One segment will always stay on while the others depend on only one or two inputs. Complete the following two-variable Karnaugh maps. D1 D0 1 0 0 2 0 D1 D0 0 2 0 1 3 D1 1 0 0 2 0 1 D1 3 2 1 0 0 2 D1 D0 3 2 1 3 1 Segment c D1 D0 1 0 0 0 1 Segment d 1 0 0 2 1 3 0 1 3 1 Segment e 0 Segment b D0 1 0 1 0 1 D0 3 1 Segment a D1 0 1 1 D0 1 0 1 Segment f Segment g Figure 3: 2 bit BCD to 7 Segment Decoder Karnaugh Maps Now that you have completed the Karnaugh maps, write down the resulting terms of the decoding logic expressions below. The expression should be SOP. a= b= c= d= e= f= g= You will be using the following two ICs to build the decoder: one 74LS08 and one 74LS04. The 74LS08 contains 4 AND gates with two inputs each. The 74LS04 contains 6 inverters. Apply your knowledge of boolean algebra to modify the logic expressions above to use just AND gates and inverters. ECE 2022 Pre-Lab 2 2.3 4 Circuit Diagram The resulting expressions for segments ‘a’ though ‘g’ can now be mapped directly into logic. Draw the logic circuit schematic for the 2 bit BCD to 7 Segment decoder and label the IC pin numbers (see attached IC pinouts for the ’04 and ’08, taken from your Floyd textbook, page 153). ECE 2022 Pre-Lab 2 5