Design of a Third-Order Sigma-Delta Modulator with Minimum

advertisement

Design of a Third-Order Σ∆ Modulator with

Minimum Op-amps Output Swing

Oscar Belotti, Edoardo Bonizzoni, and Franco Maloberti

Dipartimento di Ingegneria Industriale e dell’Informazione

University of Pavia

Via Ferrata, 1 - 27100 Pavia - ITALY

E-mail: [oscar.belotti, edoardo.bonizzoni, franco.maloberti]@unipv.it

I. Introduction

Σ∆ modulators are very popular in wireless communication

and multi-standard transceivers because of their capability to

provide high resolution with relatively low precision analog

building blocks. Methods usually exploit noise shaping and

oversampling. Portable wide-band code division multiple access (WCDMA) applications demand for A/D converters able

to provide a signal-to-noise and distortion ratio (SNDR) higher

than 70 dB over a signal bandwidth of 1.92 MHz with low

power consumption.

In order to achieve these specifications, a multi-bit thirdorder Σ∆ modulator is a good architectural choice. Low

oversampling ratio (OSR) and the minimization of the operational amplifiers (op-amps) output swing keep low the

power consumption. Typically, a third-order modulator uses

three integrators. However, suitable topological modifications

of the conventional second-order scheme achieve third-order

noise shaping by using a reduced number of op-amps, [1]. An

alternative solution is the noise coupling technique, [2], which,

however, requires an additional active block.

Low op-amps swings enable relaxed slew-rate requirements,

better linearity, lower power consumption, and allow operation

at lower power supply voltages. Various methods for reducing

the op-amps output voltage swings can be found in the open

literature, [3] [4] [5] [6].

This design obtains all the above features. The presented

modulator, designed in a 65-nm CMOS technology, uses two

op-amps to achieve a third-order noise shaping and a fully

digital solution with distributed digital feed-forward paths to

minimize the amplifiers output swings. Post-layout simulations show a SNDR of 83 dB over a signal bandwidth of

2.2 MHz (OSR = 16). The simulated overall converter power

978-1-4673-5762-3/13/$31.00 ©2013 IEEE

consumption is 2.3 mW, leading to a figure of merit (FoM)

equal to 172.8 dB (calculated with the Schreier formula) and

43.8 fJ/conversion-step (following the Walden expression).

II. Modulator Architecture

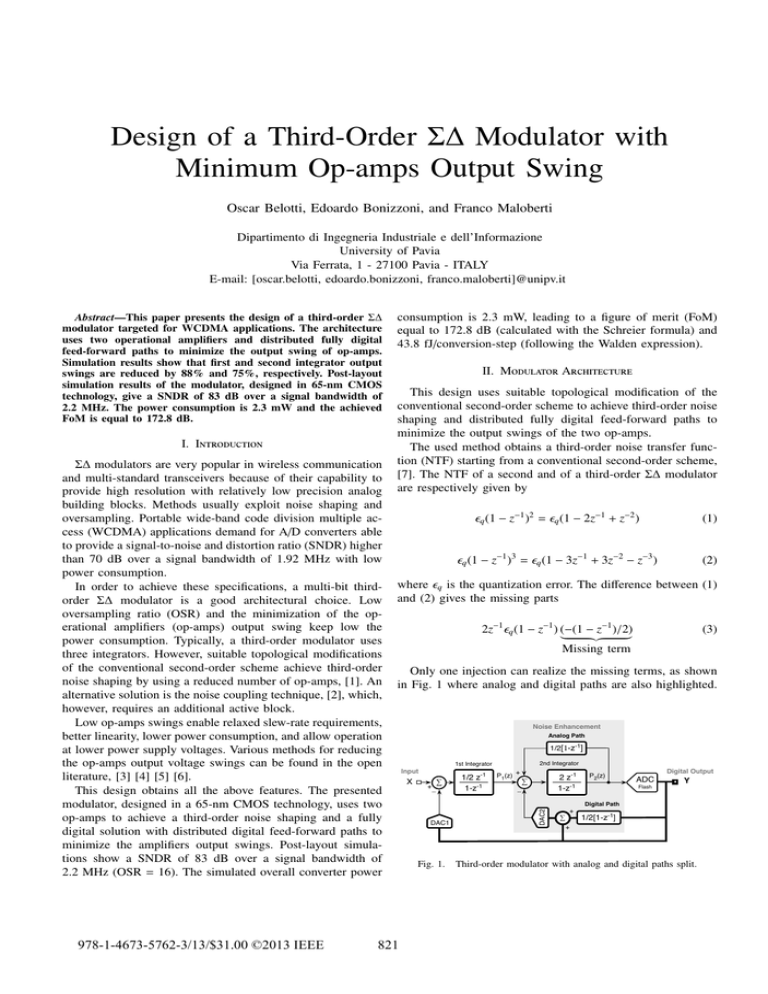

This design uses suitable topological modification of the

conventional second-order scheme to achieve third-order noise

shaping and distributed fully digital feed-forward paths to

minimize the output swings of the two op-amps.

The used method obtains a third-order noise transfer function (NTF) starting from a conventional second-order scheme,

[7]. The NTF of a second and of a third-order Σ∆ modulator

are respectively given by

q (1 − z−1 )2 = q (1 − 2z−1 + z−2 )

(1)

q (1 − z−1 )3 = q (1 − 3z−1 + 3z−2 − z−3 )

(2)

where q is the quantization error. The difference between (1)

and (2) gives the missing parts

2z−1 q (1 − z−1 ) (−(1 − z−1 )/2)

|

{z

}

Missing term

(3)

Only one injection can realize the missing terms, as shown

in Fig. 1 where analog and digital paths are also highlighted.

821

Noise Enhancement

Analog Path

1/2[1-z-1]

2nd Integrator

1st Integrator

Input

X

+_

∑

1/2 z-1

1-z-1

P1(z)

+

2 z-1

1-z-1

∑

_

P2(z)

Digital Output

ADC

Flash

Y

Digital Path

DAC1

Fig. 1.

DAC2

Abstract—This paper presents the design of a third-order Σ∆

modulator targeted for WCDMA applications. The architecture

uses two operational amplifiers and distributed fully digital

feed-forward paths to minimize the output swing of op-amps.

Simulation results show that first and second integrator output

swings are reduced by 88% and 75%, respectively. Post-layout

simulation results of the modulator, designed in 65-nm CMOS

technology, give a SNDR of 83 dB over a signal bandwidth of

2.2 MHz. The power consumption is 2.3 mW and the achieved

FoM is equal to 172.8 dB.

∑

+

1/2[1-z-1]

+

Third-order modulator with analog and digital paths split.

Auxiliary

Quantizer

Auxiliary

Quantizer

εq1

εq2

Quantized Input

Flash

X

Digital Feedforward

H2

[1-z-2]

H1

H4

1/2z-1[1+z-1]

1/2z-1[1-z-1]2

Flash

DAC4

DAC5

1st Integrator

_

Input

X

+_

∑

1/2 z-1

1-z-1

Main

Quantizer

1/2[1-z-1]

P1(z)

_

+

+_

∑

+

+

2 z-1

1-z-1

∑

∑

_

P2(z)

DAC1

DAC2

DAC

Digital Path

ADC

Flash

Digital Feedforward

H1+H4

[1-z-2]

1/2z-2[3-z-1]

DAC3

DAC4/5

Noise Enhancement

+

+

H3

Analog Path

[z-2]

εq

2nd Integrator

X

H2

H3

Analog Path

DAC3

Quantized Input

ADC

Noise Enhancement

Digital

Output

∑

_

Input

X

Digital

Summa

+_

1/2 z-1

1-z-1

∑

P1(z)

+

+_

+

2 z-1

1-z-1

∑

∑

_

1/2[1-z-1]

P2(z)

ADC

Flash

DAC2

DAC1

+

+

∑

Digital

Output

Y

Digital

Summa

Digital Path

Digital Domain

[z-2]

εq

2nd Integrator

1st Integrator

Y

Main

Quantizer

1/2[1-z-1]

DAC

ADC

1/2[1-z-1]

Digital Domain

Fig. 2.

Third-order modulator with distributed feed-forward digital paths.

Fig. 3.

Final third-order modulator block diagram.

A. Op-amps output swing minimization

The reduction of the operational amplifiers output voltage

swing decreases the overall modulator power consumption.

Indeed, output swings minimization leads not only to relaxed

slew-rate requirements, but also it ensures better performance

in terms of harmonic distortion. In addition, minimum output

swing enables the use of power efficient and compact singlestage op-amps architectures (e.g., the telescopic cascode).

The method of this design, proposed in [5], grants the

minimum output voltage swing for both operational amplifiers

by means of distributed digital feed-forward paths without

modifying the modulator signal transfer function (STF) and

NTF. The cost of the method is an extra quantizer which

digitizes the input signal.

The output of the first integrator (Fig. 1) is given by

q

q

X −1

z (1+z−1 )− (1−z−1 )2 = X · H1 − (1−z−1 )2 (4)

2

2

2

where X is the input signal multiplied by the transfer function

H1 . The main contribution to the swing of this node is given

by the input; in order to compensate for its effect, it is

convenient to process its quantized version, indicated as X.

The quantization of the input signal X is equals to X+q1 ,

where q1 is the quantization noise of the extra quantizer. The

information does not change if the quantity H1 X is added and

subtracted at the output P1 (z). The term -H1 X is then shifted

in front of the first integrator by dividing it by the integrator

transfer function. The result is an additional injection at the

input of the first integrator equal to H2 X, where H2 is (1−z−2 ).

This way, the output P1 (z) is given by:

P1 (z) =

P2 (z) = Xz−2 −q z−1 (3−z−1 )(1−z−1 ) = X·H3 −q z−1 (3−4z−1 +z−2 )

(6)

Addition and subtraction of X multiplied by the same

transfer function of the main contribution of P2 (z) obtain the

reduction of the swing of the second integrator. The quantized

input X is then multiplied by H3 and shifted in front of the

second integrator. The transfer function H3 referred to the

input of second integrator becomes H4 = 1/2z−1 (1 − z−1 )2 . The

reconstruction of P2 (z) due to the term +H3 X can be shifted

in digital domain after the main quantizer.

The overall third-order modulator with distributed feedforward digital paths is shown in Fig. 2. Combination of digital

functions and suitable topological modifications lead to the

scheme used in this design illustrated in Fig. 3.

III. Behavioral Level Simulation Results

The best trade-off between swings reduction effectiveness,

power consumption, resolution and complexity suggests to use

a 5-bit and a 4-bit flash converter in the main quantizer and

for the auxiliary quantizer, respectively. The effectiveness of

the used swing reduction technique is proved with MatlabSimulinkT M behavioral simulations. The effectiveness of the

Signal Bandwidth = 2.2 MHz | Fin = 2.18 MHz @ -2 dBFS

OSR = 16 @ FS = 70.4 MHz | VREF = 1.2 V

0.55

0.44

0.33

Amplitude (V)

1

P1 (z) = z−1 [q (1 − z−1 )2 + q1 (1 + z−1 )]

(5)

2

The output is now dominated by the quantization error q

shaped at the second order and by the auxiliary quantization

error q1 multiplied by (1 + z−1 ). The use of multi-bit solution

ensures low level swing.

The procedure can be repeated also for the second integrator, which is closed in feedback loop with the analog path

1/2(1 − z−1 ). The structure has a transfer function equal to

2z−1 /(1−z−1 )2 . The output P2 of the second integrator of Fig. 1

can be expressed as:

0.22

Output First Int. without DAA

0.11

0

Output First Int. with DAA

−0.11

−0.22

−0.33

−0.44

−0.55

0

500

1000

1500

2000

2500

3000

3500

4000

Sample

Fig. 4. Output swing of the first integrator with and without reduction

technique.

822

Signal Bandwidth = 2.2 MHz | Fin = 2.18 MHz @ -2 dBFS

OSR = 16 @ FS = 70.4 MHz | VREF = 1.2 V

0.3

0.25

VSS

0.2

Amplitude (V)

0.15

Output Second Int. without DAA

VDD

Vin

0.1

0.05

0

Output Second Int. with DAA

VDD

−0.05

Vout

VSS

Low VTH

HIGH VTH

−0.1

−0.15

−0.2

−0.25

−0.3

Fig. 7.

0

500

1000

1500

2000

2500

3000

3500

Full swing composite switch.

4000

Sample

Fig. 5. Output swing of the second integrator with and without reduction

technique.

technique is tested by applying an input sine wave at 2.18 MHz

(close to the signal bandwidth limit = 2.2 MHz) with an

amplitude of -2 dBFS . The oversampling ratio is 16 and

consequently the sampling frequency is 70.4 MHz.

Fig. 4 shows the output voltage swing for the first integrator

with and without swing reduction technique. The output swing

goes down from ±0.504 V to ±0.065 V, which corresponds

to a swing reduction of 88%. For the second integrator, the

benefit is approximately 75%, from ±0.28 V to ±0.076 V, as

shown in Fig. 5. As an additional benefit, thanks to this swing

reduction at the output of the second integrator, the number of

comparators used in the main quantizer can be reduced from

31 to only 9 still granting the 5-bit quantization, thus saving

area and power.

VDD

M37

VDD

M35

VDD

+_ _

+

M36

OP-AMP1

VOUTN

M33

M34

OP-AMP2

_ +

+_

VSS

VINP

M38

VCMFB1

M31

VSS

Vbias1

VSS

VDD

VDD

IV. Circuit Implementation

The fully differential switched-capacitors implementation of

the modulator has been realized in a 65-nm CMOS technology.

As mentioned, low output swing allows using single-stage

op-amp scheme. This design uses the conventional telescopic

scheme with gain boosting shown in Fig. 6. The auxiliary

amplifiers (OP-AMP1 and OP-AMP2) are conventional folded

cascode schemes with p-channel and n-channel input stage,

respectively. The supply voltage is 1.2 V. Different bias

currents (250 µA for first op-amp and 280 µA for the second)

allow achieving the slightly different gain and bandwidth

requirements. The first op-amp has a 94-dB DC gain and 240MHz GBW while the second obtains 90-dB gain and 270-MHz

bandwidth.

To limit the sub-threshold off current leakage of analog

switches that can cause analog performance degradation, this

design uses the composite switch scheme given in Fig. 7.

The scheme requires the use of transistors with low and high

threshold voltage. Two high VT H complementary transistor are

used in parallel with a series transmission gate. The high gate

ensures good conduction when the input signal, Vin , is close to

the rails, while at middle rail series transmission gate conducts

well, [8].

The voltage comparator used in the two flash ADCs consists

of a preamplifier followed by a regenerative latch. The nonconventional fully differential preamplifier is shown in Fig. 8.

Vn and V p are connected to the input of the latch (not

VOUTP

VDD

VSS

M32

M7

VSS

VINN

M10

Vn

M30

VSS

VSS

M8

VDD

Va

VDD

M9

M12

Vinp

Vb

M3

M4

VSS VSS

M1

VSS

Vrefp Vrefn

M5

VSS VSS

M2

VSS

M6

Vinn

Vb

VSS

Vp

M11

VSS

VSS

Fig. 6.

Gain boosted telescopic operational amplifier.

Fig. 8.

823

Schematic diagram of the comparator preamplification stage.

Matrix Array (32*32)

Implementation

Example A + B = Y 10 + (-1) = 9

From

Auxiliary Quantizer

B

15

14

0

1

CLK1

IN1

-2

-3

IN3

IN1

IN3

IN1

IN3

-15

-16

IN1

IN3

OUT1

OUT2

OUT1

OUT2

OUT1

OUT2

OUT1

OUT2

12

3

CLK1

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

OUT1

OUT2

OUT1

OUT2

OUT1

OUT2

OUT1

OUT2

11

10

4

CLK2

5

CLK1

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

IN2

IN1

IN1 CLK2

IN3

9

OUT1

OUT2

OUT1

OUT2

OUT1

OUT2

OUT1

OUT2

8

6

CLK2

7

CLK1

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

OUT1

OUT2

OUT1

OUT2

OUT1

OUT2

OUT1

OUT2

1

0

14

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

-15

15

CLK1

CLK2

OUT1

OUT2

OUT1

OUT2

OUT1

OUT2

OUT1

OUT2

GND

CLK2

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

IN2

IN1

IN1

IN3

CLK1

-16

IN2

A

GND

CLK1

OUT1

OUT2

OUT1

OUT2

OUT1

OUT2

OUT1

OUT2

CLK2

IN2

IN1

IN2

IN1

IN2

IN1

IN2

IN1

15 Y

14

13

12

Output Modulator

-1

13

2

CLK2

reduced by 88% and 75%, respectively. This swing reduction

allows using power efficient telescopic schemes for both

amplifiers. Post-layout simulations confirm the effectiveness

of the approach.

From

Main Quantizer

References

11

10

9

8

CLK2

IN1

OUT1

IN3

OUT2

GND

GND

IN1

IN3 CLK1

OUT1

OUT2

IN2

IN1

IN1 CLK2

IN3 CLK1

OUT1

OUT2

Fig. 9.

IN2

IN1

IN1 CLK2

IN3 CLK1

OUT1

OUT2

IN2

IN1

IN1 CLK2

IN3 CLK1

OUT1

OUT2

IN2

IN1

IN1 CLK2

IN3 CLK1

OUT1

OUT2

IN2

IN1

IN1 CLK2

IN3 CLK1

OUT1

OUT2

IN2

-15

IN1 CLK2

-16

Implementation of the switches matrix.

shown) by means of switches which are opened during the

regeneration phase in order to limit the kickback effect.

DAC, DAC1 and DAC2 of Fig. 3 are realized with a single

Kelvin divider with 32 levels. A single resistive string provides

the required 16 levels for DAC3 and DAC4/5. The sizes and

value of the unity resistance ensure the required accuracy

without the need of trimming or calibration and speed at a

reasonable cost of area and power consumption. In addition,

the use of the same resistive string to generate the differential

reference voltages cancels at the first order the error caused

by a gradient, [7].

A barrel shifted architecture based on a matrix of simple

switches (Fig. 9) realizes the digital addition of the output of

the main and auxiliary quantizer (see Fig. 3), saving digital

power at the cost of an affordable increased chip area.

[1] E. Bonizzoni, A. Pena Perez, F. Maloberti, and M.A. Garcia Andrade, “Two Op-amps Third-Order Sigma-Delta Modulator with 61 dB

SNDR, 6 MHz Bandwidth and 6 mW Power Consumption”, Proc. of

IEEE European Solid-State Circuits Conference (ESSCIRC), pp. 218221, Sept. 2008.

[2] K. Lee, M. R. Miller, and G. C. Temes, “An 8.1 mW, 82 dB DeltaSigma ADC With 1.9 MHz BW and -98 dB THD”, IEEE Journal of

Solid-State Circuits, pp. 2202-2211, Aug. 2009.

[3] K. Y. Nam, S.-M. Lee, D.K. Su, and B. A. Wooley, “A Low-Voltage

Low-Power Sigma-Delta Modulators for Broadband Analog-to-Digital

Conversion”, IEEE Journal of Solid-State Circuits, vol. 40, pp. 18551864, Sept. 2005.

[4] A. A. Hamoui, M.Sukhon, and F. Maloberti, “Digitally-Enhanced HighOrder Σ∆ Modulators”, Proc. of IEEE International Conference on

Electronics, Circuits, and Systems (ICECS), pp. 1115-1118, Aug. 2008.

[5] H. Caracciolo, E. Bonizzoni, F. Maloberti, and G. S. La Rue, “Digitally

Assisted Multi-Bit Σ∆ Modulator”, Proc. of IEEE International Symposium on Circuits and Systems (ISCAS), pp. 3993-3996, May 2010.

[6] J. De Maeyer, P. Rombouts, and L. Weyten, “Efficient Multibit Quantization in Continuous-Time Sigma-Delta Modulators”, IEEE Transactions on Circuits and Systems I - Regular Papers. vol. 54, pp. 757-767,

2007.

[7] A. Pena Perez, E. Bonizzoni, and F. Maloberti, “A 88-dB DR, 84 dB

SNDR Very Low-Power Single Op-Amp Third-Order Σ∆ Modulator”,

IEEE Journal of Solid-State Circuits, vol. 47, no. 9, pp. 2017-2118,

Sept. 2012.

[8] S. Bazarjani and W. M. Snelgrove, “Voltage SC Circuit Design with

Low Vt MOS-FETs”, Proc. of IEEE International Symposium on

Circuits and Systems (ISCAS), pp. 1021-1024, May 1995.

V. Post-Layout Simulation Results

Fig. 10.

0

−20

−40

PSD

PSD(dB)

[dB]

The Σ∆ modulator has been implemented in a 7-metal

levels 65-nm CMOS technology. Fig. 10 shows the layout of

the circuit. The chip area is 1770 × 400 µm2 . The sampling

frequency is 70.4 MHz and the OSR is 16.

Fig. 11 shows the post-layout simulated output spectrum

of the modulator. The -2 dBFS input signal is at 326 kHz.

The achieved SNDR is 83.27 dB (equivalent to 13.54 bits)

over a signal bandwidth of 2.2 MHz. Third and fifth harmonic

tones are at -94 dBFS and -100 dBFS , respectively. The converter dynamic range is 88 dB. The simulated overall power

consumption is 2.3 mW, leading to a figure of merit (FoM)

equal to 172.8 dB (calculated with the Schreier formula) and

43.8 fJ/conversion-step (following the Walden expression).

A third-order Σ∆ modulator realized with two minimum

output voltage swing op-amps has been presented. Simulation

results show that first and second integrator output swings are

824

Signal Bandwidth = 2.2 MHz | Fin = 326 KHz @ -2 dBFS

OSR = 16 @ FS = 70.4 MHz | FFT points = 4096

Noise filtered

SNR = 83.27dB

Rbit = 13.54 bits

−60

rd

th

3 HD 5 HD

−80

−100

-60 dB/decade

−120

−140

−160

−180

VI. Conclusion

Chip layout. The active area is 1770 × 400 µm2 .

Fig. 11.

Input Signal Bandwidth fB

105

10 6

Frequency [Hz]

Frequency

(Hz)

107

Post-layout simulation of the modulator output spectrum.