New Graphical I Signatures Reduce Defect Level and Yield Loss

advertisement

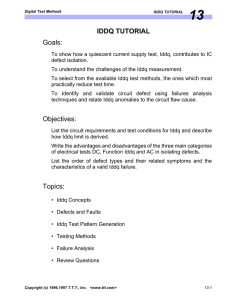

New Graphical IDDQ Signatures Reduce Defect Level and Yield Loss (U. S. Patent Pending) Lan Rao Michael L. Bushnell Vishwani Agrawal ECE Dept., Rutgers U., Piscataway, NJ IDDQ Signatures 1 IDDQ Testing VDD = 5V IDD Ground IDDQ fault Ref. Chakravarty and Thadikaran, 1997 IDDQ Signatures 2 IDDQ (microA) vs. Vector # A good chip A bad chip IDDQ Signatures 3 Two Proposed Approaches: New way #1 Use 135 IDDQ test vectors, instead of 10-20 vectors in real production line, collect all current measurements and plot current as function of test vector index. Use classifier software running on Automatic Test Equipment to classify chip as good or bad. Without using ‘stuck-at fault’ voltage test, but keeping the other voltage tests. New way #2 Only use graphical IDDQ testing method defined above. Potentially large cost saving for VLSI chip manufacturing test. IDDQ Signatures 4 Economics Analysis* Method # Measurements Existing Current & With New Graphical Voltage Testing Current Testing 8023(stuck-at)+53k 135(IDDQ)+15232(delay) (functional)+15232(delay) +53k(functional) + 20(IDDQ) Use Only Graphical Test 135(IDDQ) Test time 14.55s 10.23 s 2.90s Production test cost 5 cents/s X 14.55s = 72.8cents 5 cents/s X 10.23s = 51.2cents 5 cents/sX2.9s= 14.5cents Cost savings 0% 30.0% 80.1% % Defective chips found 98.30% 99.85 % 96.1% Pattern gen. Difficult Simpler Much simpler Diagnosis Complex Complex Complex *With help from Dr. Phil Nigh, IBM. IDDQ Signatures 5 New Classification Features The shape of the entire curve of current measurements – # of bands that measurements cluster into. Width and separation of bands. Current glitch or smearing detection among all IDDQ measurements. IDDQ Signatures 6 IIDDQ Distribution Over Vectors is not Gaussian # of IDDQ values 1 Good Devices Bad Devices IDDQ Only 5684 1592 351 2 5674 2429 546 3 487 1144 104 4 12 367 31 >4 1 44 0 IDDQ Signatures 7 Classification of DUT Good devices Devices passing all tests and all test steps. Devices that fail wafer probe test, but pass packaged test and burn-in, (poor wafer probe registration). Bad devices Devices that failed the tests other than the IDDQ test. Devices with extremely high IDDQ current. IDDQ only • Devices that failed on the IDDQ test with less than the absolute IDDQ threshold. IDDQ Signatures 8 Good vs. Faulty Chip (Single Band) Single band of a good chip Smeared (noisy) single band of a bad chip IDDQ Signatures 9 Good vs. Faulty Chip (Single Band with Spike) Good Chip Plot Faulty Chip with Noise Spikes IDDQ Signatures 10 Good vs. Faulty Chip (Multiple Bands) Good 2 Band Chip Faulty 2 Band Chip with Smearing IDDQ Signatures 11 Comparing IDDQ Test Methods Statistics (A) Method Singlethreshold Test Escape (8) Overkill (8) Test escape (25) Overkill (25) Test escape (450) Overkill (450) 6.4 % 1.6% 6.8% 2.2% 7.5% 2.3% Current difference 35.3 % 3% 34% 3% 35% 3.1% IDDQ (4 A) IDDQ (ó =0.35) Graphical IDDQ 8.9 % 7.3 % 5.0 % 1.1% 8.6 0.8% 8.6% 1.0% 6.6% 7% 6.7% 7.6% 6.8% -2.8% 5.4% -2.7% 5.97% -2.5% Observation: The absolute threshold value is not critical for this technique. IDDQ Signatures 12 Test Method Efficiencies Statistics Test Method % Bad Chips Detected 8 A 450 A IBM Functional Test IBM Stuck-at Test IBM Delay Test IBM IDDQ Test Graphical IDDQ Test 52.6 % 71.3 % 70.3 % 93.6 % 96.1 % 61.5% 83.4% 82.2% 93.5% 96.1% IBM (functional+ stuck-at+delay) 75.8% 88.6% IDDQ Signatures 13 Test Vector Set Truncation Results # of IDDQ vectors Good devices out of 11,858 Bad devices out of 5,576 IDDQ only devices pass out of 1,032 # 1 (125) 11,711 5,229 167 # 1 + # 2 (135) 11,715 5,240 165 # 1 + # 3 (185) 11,715 5,235 154 # 1 + # 2 + # 3 (195) 11,719 5,243 153 50 random 11,657 5,152 222 100 random 11,726 5,168 176 140 random 11,735 5,209 172 Proper selection of test vector set can further improve the test quality. IDDQ Signatures 14 Conclusion Gaussian distribution of IDDQ measurements may not be true. We present a new way of IDDQ testing with lower test escape and lower yield loss (overkill rate). The new method does not rely on a single threshold or a single delta threshold, but on the shape of the measurement set, hence it is promising for deep submicron technology; can replace at least some voltage tests; the accuracy can be further improved by careful choice of the test vector set. IDDQ Signatures 15 Thank you! IDDQ Signatures 16