Faculty:

FACULTY OF ELECTRICAL ENGINEERING

Review

Course

: SPECIALIZED 3RD YEAR LABORATORY Release Date

Course Code : SKEL 3742

Last Amendment

Procedure Number

:

: 8 February 2015

: 8 February 2015

:

FAKULTI KEJURUTERAAN ELEKTRIK

UNIVERSITI TEKNOLOGI MALAYSIA

KAMPUS JOHOR BAHRU

JOHOR

SKEL 3742

VLSI SYSTEM DESIGN LAB

Date Display System using FPGA

Prepared by :

Name: Izam Bin Kamisian

Signature & Stamp :

Date:

Approved by: Head of Department

Name: Dr. Nasir Bin Shaikh Husin

Signature & Stamp :

Date:

© 2014 Universiti Teknologi Malaysia – All Rights Reserved

Project Introduction

In a standard calendar system, the number of days in a month is either 28, 29, 30 or 31. For

example, the number of days for February is 28 for common year and 29 for leap year. Leap years

are all the years divisible by 4, except that years divisible by 100 are not leap years. Years

divisible by 400 are also leap years. As an example, the year 1900 is not a leap year because it is

divisible by 100 but not divisible by 400.

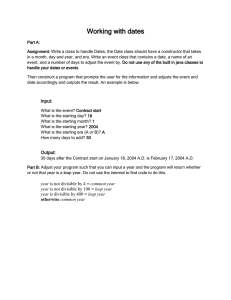

In this project, you are required to design a system which can display date in the format

of DD/MM/YYYY. The date must follow standard calendar system where you have to consider

the number of day in a month whether 28, 29, 30 or 31 days, 12 months in a year. Part of the

system is a circuit that can determine the number of days in a month and whether a given year is a

leap year. The system should able to tune each digit of D, M or Y. The digit to be tuned is

selected by control circuit. Figure 1 shows an example of a Date Display System block diagram.

The objectives of this project are:

1. To design the system using combinational and sequential logic design.

2. To verify functionality of the system using Altera Quartus II software.

3. To prototype and demonstrate the system using Altera DE2 FPGA board.

Project Task

The system must be prototyped and demonstrated using Altera DE2 FPGA board. The system

should be able to display date in DD/MM/YYYY format on the 7 segment display on the FPGA

board. A single LED on the FPGA board must be lighted on when the year (YYYY) is a leap

year. The system must able to operate in either normal or tune mode. In normal mode, the system

count as normal calendar system when push button 1 (PB1) is pushed. In tune mode, each digit D,

M or Y can be tuned one digit at a time using PB1 and PB2. PB1 is to trigger the system to count

and PB2 is to select which digit to be tuned or normal operation. The selected digit to be tuned

must be blinked.

Identify inputs and outputs of your system, encoding and decoding method, circuit

topology and suitable algorithm to be used. Design the system and verify its function using

Quartus II CAD Tools. Prototype and demonstrate your system using DE2 FPGA board. Refer to

the VLSI Student Pack tutorial to help you to implement this project.

For the first session of your lab, write a proposal about the project containing system

block diagram and a design methodology to implement the system. Finally, a report with the well

2

presented design steps, simulation results and FPGA prototyping methodology are expected to be

produced at the end of the project after the third session of the lab.

DD

MM

YYYY

7 Segment Decoder

LY flag

Day flag

counter

Control Circuit

PB1

PB2

Figure 1: Date Display System

3