Lecture 37

Lecture #37: Memory

• Last lecture:

– Transmission line equations

– Reflections and termination

– High frequency measurements

• This lecture:

– Static Ram

– Dynamic Ram

11/29/2004 EE 42 fall 2004 lecture 37 1

Memory types

• In addition to registers, there is usually a need in digital logic devices for a denser

(and therefore cheaper) means of storing information in larger amounts.

• The main memory types are known as

RAM (Random Access Memory) as contrasted with long shift registers from which information can only be extracted or added in sequence.

11/29/2004 EE 42 fall 2004 lecture 37 2

RAM

• In a RAM, an address is provided to a block of logic, along with an address strobe and a write signal line.

• The memory block then either reads a block of bits and puts it onto a bus, or writes the data from the bus into the indicated area of memory.

11/29/2004 EE 42 fall 2004 lecture 37 3

Types of memory

• SRAM (Static RAM) is a memory which is essentially an array of flip flops. It can be very fast, and is integrated with logic.

• DRAM (Dynamic RAM) is a dense memory which uses a single capacitor controlled by a switch to store a bit. Dram must be rewritten after a write, and must be refreshed periodically.

11/29/2004 EE 42 fall 2004 lecture 37 4

Other types of memory

• Read only memory (ROM) is a memory whose content is fixed at manufacture, and thus can only be read.

• Content addressable memory (CRAM) is memory which can be addressed, at least in part by its contents, rather than an address.

• E 2 memory (electrically erasable) is memory which can be read and written, but whose content is nonvolatile. Writing is often much slower than reading

11/29/2004 EE 42 fall 2004 lecture 37 5

RAM logical organization

Column Decoder

…

Read/Write

D

Q

Address lines

Memory array

Address strobe

Note that the number row decoder lines and column lines goes like the square root of the memory size

11/29/2004 EE 42 fall 2004 lecture 37 6

SRAM

• Cache uses SRAM : Static Random Access

Memory

– No refresh

– Size 6 transistors/bit

– Fast, can be optimized for speed or area reduction

– Compatible with dense logic, so can be integrated with microprocessors with no extra masks

11/29/2004 EE 42 fall 2004 lecture 37 7

Static RAM (SRAM)

• Six transistors in cross connected fashion

– Provides regular AND inverted outputs

– Implemented in CMOS process

11/29/2004

Single Port 6-T SRAM Cell

EE 42 fall 2004 lecture 37 8

SRAM cell

• Each cell of an SRAM is a pair of cross connected small inverters

• As long as power is supplied, the latch will hold the value.

• When the row line is held high, the outputs are driven with the contents of the memory.

• The latch is written by using a more powerful driver on the column lines to overcome the smaller transistors in the latch which forces the desired state.

11/29/2004 EE 42 fall 2004 lecture 37 9

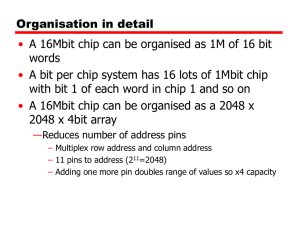

DRAM

• Main Memory is DRAM : Dynamic Random

Access Memory

– 1 transistor

– Dynamic since needs to be refreshed periodically

(8 ms, 1% time)

– Addresses divided into 2 halves (Memory as a 2D matrix):

• RAS or Row Access Strobe

• CAS or Column Access Strobe

11/29/2004 EE 42 fall 2004 lecture 37 10

Dynamic RAM

• SRAM cells exhibit high speed/poor density

• DRAM: simple transistor/capacitor pairs in high density form

Word Line

C

.

.

.

Bit Line

Sense Amp

EE 42 fall 2004 lecture 37 11/29/2004 11

Basic DRAM Cell

• Planar Cell

– Polysilicon-Diffusion Capacitance, Diffused Bitlines

• Problem: Uses a lot of area (< 1Mb)

• You can’t just ride the process curve to shrink C (discussed later)

Capacitor

11/29/2004

Metal word line poly n

+ poly n

+

Inversion layer induced by plate bias

(a) Cross-section

SiO

2

Field Oxide

M1 word line

Diffused bit line

Polysilicon

Polysilicon plate gate

(b) Layout

Used Polysilicon-Diffusion Capacitance

Expensive in Area

EE 42 fall 2004 lecture 37 12

DRAM Operations

• Write

– Charge bitline HIGH or LOW and set wordline HIGH

• Read

– Bit line is precharged to a voltage halfway between HIGH and LOW, and then the word line is set HIGH.

Word

Line

– Depending on the charge in the cap, the precharged bitline is pulled slightly higher or lower.

– Sense Amp Detects change

C

.

.

Bit Line

• The signal is decreased by the ratio of the storage capacitance to the bitline capacitance

– Increase density => increase parasitic capacitance

Sense

Amp

– As geometries shrink, still need large bit capacitance

11/29/2004 EE 42 fall 2004 lecture 37 13

Advanced DRAM Cells

• Stacked cell (Expand UP)

11/29/2004 EE 42 fall 2004 lecture 37 14

Advanced DRAM Cells

• Trench Cell (Expand DOWN)

Cell Plate Si

Capacitor Insulator

Storage Node Poly

2nd Field Oxide

Refilling Poly

Si Substrate

11/29/2004 EE 42 fall 2004 lecture 37 15

DRAM logical organization

(4 Mbit)

11

Column Decoder

…

Sense Amps & I/O

D

Q

A0…A10

Memory Array

(2,048 x 2,048)

Word Line

• Square root of bits per RAS/CAS

11/29/2004 EE 42 fall 2004 lecture 37 16

Bit line

DRAM sense amp

+V enable enable

Both precharged to ½ V

Data out enable enable

EE 42 fall 2004 lecture 37 11/29/2004 17

DRAM sense amplifier

• The reason that DRAM is slow, is that a very small charge is captured on the capacitor, and the small voltage change on the line must be sensed.

V

Charge dumped to bit line

Precharge →

Sense amp decides 0 or 1

EE 42 fall 2004 lecture 37 time

11/29/2004 18

DRAM/SRAM tradeoffs

• By it’s nature, DRAM isn’t built for speed

– Response time dependent on capacitive circuit properties which get worse as density increases

• DRAM process isn’t easy to integrate into CMOS process

– DRAM is off chip

– Connectors, wires, etc introduce slowness

– IRAM efforts looking to integrating the two

• Memory Architectures are designed to minimize impact of DRAM latency

– Use dram for high density, store data which is used often in smaller, higher speed SRAM cache.

11/29/2004 EE 42 fall 2004 lecture 37 19

FLASH Memory

• Floating gate transistor

– Presence of charge => “0”

– Erase Electrically or UV (EPROM)

• Performance

– Reads like DRAM (~ns)

– Writes like DISK (~ms). Write is a complex operation

11/29/2004 EE 42 fall 2004 lecture 37 20

More esoteric Storage

Technologies?

• Tunneling Magnetic Junction RAM (TMJ-RAM):

– Speed of SRAM, density of DRAM, non-volatile (no refresh)

– New field called “Spintronics”: combination of quantum spin and electronics

– Same technology used in high-density disk-drives

11/29/2004 EE 42 fall 2004 lecture 37 21

Tunneling Magnetic Junction

11/29/2004 EE 42 fall 2004 lecture 37 22