Document 13524814

advertisement

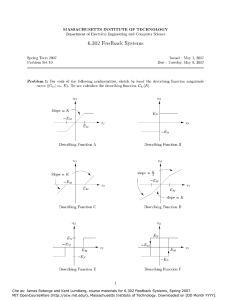

MASSACHUSETTS INSTITUTE OF TECHNOLOGY Depart,rnent of Electrical Engineering arlrl Cornpllt,er Science Spring Terrr~2007 PLL Design Prol~lern 111illis la11 you will irlvestigate phase lock loop (PLL) operation using the CMOS 4046 ir~tegraterlcircuit. two (lifferent phase rletectors and a VCO. It also in<:l~l(ies a. zerler (iiocle referer~(:ef ~ pnwer r s111111ly It cor~tair~s reglllatior~and a 1111fferf ~ t,lle r (ie1110d111at,nro ~ t , p ~Tlle ~ t . I I S P ~I I I I I S ~s111111lythe 10011 filter. Tlle l ~ i g input, l~ of the 1016 ~ r ~ a kiteeasy to select ext,errlal <:ornponents. irnpe(ian<:esand lorr o ~ t , pirnpe(ian<:es ~~t Notes 1. Part,s 3 and 1of illis lat] rrlust l)e (iernonstrat,e(it,o a. T.A. The T.A may ask to see your res~lltsfrorr~t l ~ e prececling parts of t l ~ elal]. Have this ir~forrr~at,ior~ ready. 2. This la11 is cornplicaterl. Be sure illat yo^^ ~~n(ierst,an(l llorv the circuits are s~~pposecl t,o work l~efore corning i r ~ t ot,lle lal]. Do not try to t111ilr1sorr~etl~ir~g t,llat yo11 l ~ a v enot fillly analyze(i. Rear1 illis erltire l~eforel~eginningt,o work on it. assigr~rr~er~t 3. Data t,akerl in Part 1 will l ~ nee(iecl e in order t o complete your rlesigns in t l ~ erest of the lrxl). t,herefnre. rlo t,l~ispart carefillly. 1. Harlrlle t l ~ e1016 \%-it,hcare. CMOS integrat,e<lcircuit,~are easily (iest,roj~r(i..Avoid stat,ic (iischarges. Use a 1OkR r e s i s t ~ rto <:ol1111ethe sigrlal gerlerat,nr t,n t,lle PLL. Turn off the sigrlal gerlerator l,rforr t~lrningoff po\%-ert,o t,lle 1016, or else you will porrer 111)the er~tirecircuit frorr~t,lle sigrlal i n p ~ ~.Avoicl t. or t,lle sl~pply.d TTL gat,e can rvithstan(i t,l~iskind of at111se.t ~ n CMOS sllort,ir~gthe o ~ ~ t p ~tol tgro~mcl s t t, to drive capacitive loads. carlrlot (be careful of loose wires). CMOS rloes riot have t,lle o ~ l t p l ~strengt,h I.is sl~ol~lrl t ~ e<:onnecterlto grounrl, u 1 ; sho~~lcl l ~ ceonnect,e<lt,o 5\', and pi11 5 s11o11l(il)e <:onnecterl to gro~mcl(ot,herwise the VCO in inhil~it,e(l). 1 VCO Operation Read t,lle circuit clescript,ion in t,lle ~latasheet,.Tlle VCO cor~st,ar~t ( I l ( j in ra<lians/sec-volt,)is t l ~ erat,io of t,lle 1:hange in operat,ing freq~lencyt,o t l ~ ecllar~gein input volt,age (on pin 9). 1Ieas11re IG,, t,llat is, graph t l ~ e output freq~lencyversus the i11put voltage. 13e sure that your data covers t l ~ erange frorr~S kHz t o 50 kHz. Make t,lle rr~easl~rerr~er~ts with variol~sval~les' of R1. Ra, arlrl C. .A-\l~proxirnately. how is Il(j relater1 t,o R I , Ra. and C'! 1Ieas11ret,lle rise and fall t,irrles of t,lle VCO o ~ ~ t pIr~vestigate ~~t. the effects of capacitive loading. 2 Passive Loop Filters The loop filter is placed t~et,weent,lle phase detect,nr o u t , p ~ rxrld ~ t the VCO i ~ ~ p u tThis , . filt,er at,terl~~at,es the 11igl1freq~lencyharrnoni<:s present in t l ~ ephase clet,e<:toro ~ l t p l ~ tI, t. also corltrols loop (lynarni<:s. Ofter~a simple RC filt,er mill fim<:tiona(ieql~at,ely.These (lesigns avoirl err11)arassinglevel sl~ift,ir~g and o ~ l t p l lirniting ~t ~ ~ r o t ~ l eirlllerer~t rns i11 act,ive filter desigrls. 011the nther hand. act,ive filters rrlaji offer s1111erinrI I ~ I . ~ O ~ I ~ I ~ I I < : ~ . 'TTSDER N O (:IR(:Tl\IST.4N(!ES nsr R I or R2 less ahsll 30kCl. 1 Cite as: James Roberge, course materials for 6.302 Feedback Systems, Spring 2007. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY]. 2.1 Phase Comparator I1 Before contim~ing.consicler t l ~ eo u t , p ~of ~ t phase cornparator I1 of the 4046. The o u t , p ~is ~ ta t,ristat,e rlevice. This causes a rerl~~ctior~ of the ripple \%-1le11t,lle loop is lockerl. Inst,ea<lof a. 50%) 1;1111tyc:yc:le t ~ e a trlot,e at t,~%-i<:e t l ~ efim~larnental.illere is no t ~ e a trlot,e at all. Unfort~lnately.rvller~orle wishes to corlstr~lcta. l)lo<:k cliagrarn for t,lle loop, Ilo is rlot \%-ell-spe<:ifierl. W l e n eitller the 11p11er01 lo~verdriver is 011, t,lle 011tp11t lnoks like a voltage source. l111t \%-henthe o u t , p ~is ~ tfloat,ing, it is essentially a currerlt sollrce (a sollrce of 0 arnps). Tllerefore t l ~ evrx111e nf ICLI will rlepencl on t,he specific filter. Cnnsi(br Figure 1. Figure 1: Pllase <:ornparatorI1 o u t , p ~ ~ t So t l ~ ephase cornparat,or o u t , p ~ is ~ tr;po = +SV \%-hent,lle i~pperdriver is on, = OV rrller~the lo~ver driver is on. and = o u when the phase cornparator is in t l ~ eopen stat,e. ni. can fir111the average val~le nf t,l1e ollt,pllt: for for 0, > 0 0, < 0 Note illat the val~leof ICLI <lepen(ison t,lle vdue of r;o. This rrlakes the rr~atllerr~at,ics of t,lle loop rm11:h rrlore confilsing. In fact Ilo is (lifferent for positive and rlegative phase errors when o u is riot 2.5 volts. In Ire can modify the o ~ l t p l ~tot , yielrl a fixed val~leof I l o . To (lo this we can put, order to get a ilsal~leo~ltpl~t,. an act,ive elerrler~tin to define t,lle va111e nf l i T~V ~ I ~ Ithe I O I I ~ ~ is I I OII~II. ~ I11 t ) o t l ~Figures 2 and 4 t,lle open v:x111e is defi~ledas 2.: vnlt,~\%-hic:hleads t,n an eq~lalval~leof ICLI for positive arlrl negative 0,. If yo^^ use phase cornparator I1 \%-it,h just an RC net,work, l ~ sure e to realize that t,lle loop dynamics may l)e consi(ieral11y <:ornprorr~ise(l at ext,rerrles of lock range. .isirnple se<:onrlorder PLL wit11 '.passive" loop filt,er is illl~st,raterlin Figure 2. Phase cornparator I1 is ~lsecl. IJ-llen t,lle loop is lo<:kecl,t,lle average phase rletector o ~ ~ t volt,age p ~ ~ tis r;o = 2.5 + 2.S(0,/2~) volt,s. The ir~crerr~rr~t,al phase rletector gain corlstar~tis t,llerl Ilo = 2 . S / 2 ~iivolts/ra(iian. Consi(ier the folio\%-ing specific:.1' t 'lorls: loop crossover frerl~lency *., = 1000 ra(i/s @,,,= 4S0 phase rnargin center freql~ency f o = 19 kHz phase detect,nr I1 IYhere Ire (lefine the cer~t,erfreqllrncy, fi,, as the YCO o u t , p ~freq11e11c:y ~t rnller~pin 9 is 2.5 volts. Using t,he t,opology illl~st,raterlin Figure 2. rlesign arlrl l ~ ~ l i la( icircuit that rrleet,s t,l~eses1)e~:ifications2. D o c ~ ~ r r ~~e~r0~1tdesig11 wit11 t)lo<:k(iirxgrrxrr~sand Borle plot,s of t l ~ err~ag~~it,l~(le 11 and angle of t,lle loop t,ransrnission. W l a t is the steady stat,e phase error and lock range'! How (in your pre(li<:tionsarlrl rnean~rernents <:ornpare? Tlle phase rnargin of t l ~ eloop may l)e ded~~c:e(i frnrr~rrleasIlrerrleIlts nf the stel) ~ ~ S I I O I InfS ~t,lle 10011. One techniq~leis t,o ap111y a F\I signal t,o t l ~ einpilt arlrl look at t l ~ e(ierr~orI~~lat,e~l o ~ t , p ~S~~ecificallj., ~t. use "Hint,: lrr R ~ C = I I ms. Then C' and R I arr chc,srn to srr while R2 drtrrminrs 2 Cite as: James Roberge, course materials for 6.302 Feedback Systems, Spring 2007. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY]. Figure 2: '.Passive" loop filter a square wave to rrlorl~~lat,e t l ~ efreq~~ency of t l ~ efim<:tion generat,or r r l ~ i c lyo^^ ~ are using for yo1n ~ I I ~ I I I ~ , ~ . ~t Measl~rethe risetirr~eand 11eak overshooot. Are tllese resl~ltsc:o~r~pr%tit)le Ol~servet l ~ eVCO i n p ~ voltage. ~vit,ha secon(i order systerrl wit11 the spe1:ified cr~ssnverfre(l~~er~(:y r%rldphr%se1rlargirlY NOTE: the freq~~ency (leviation sho111(it)e very srrlall so illat t l ~ ePLL does not l~reaklock. Figure 3: Lag loop filter Tlle loop filter is replace(i 11~7t l ~ elag rletrvork illl~st,raterlin Figure 3. It will r%llo~v yo11 t,n set IIo and w, in(iepenr1ently. Hence, t,lle loop may l~avea. rvide lock range (as rleterrr~ir~erl t)y I') and a rlarrow l)an~l\%-i~lth. Design and t)~~ilrl a. circuit to rrleet t,lle follorrir~gsl~ecificat,ions: loop crossover freql~ency phase rr~argin center freql~ency lock range phase detect,nr w, = $, fi, 1000 rarl/s = 15" = 19 kHz 9 kHz to 29 kHz I1 111cl11rlethe appropriate Dorle plots. Tlle lag filter cloes rlot provirle rm11:h a t , t e r ~ ~ ~ a tofi otrl~~ elligl~freq~lencyripple frorr~t l ~ ephase detect,nr. This is eviclent when yo^^ ot)serve t,lle voltage at the YCO input (pin 9). Place a capacitor across Rq in order "If f r r q ~ l r n ~generators .y srr in short supply. c<~nsidrr using thr V(!O from am~ahrr4Ol(i. Cite as: James Roberge, course materials for 6.302 Feedback Systems, Spring 2007. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY]. t,o increase t l ~ elligl~fre(l~len<:y at,temlation. If this pole is 11lacecl1)eyoncl the loop crossover freclllency. there will t)e rlegligil~le<:11>~11ge in t,lle E l 1 step respnrlse, except, t,llat,t , l ~ 11ig11 e freq~lerlcyt,eet11 will l ~ re~rlnvecl. e Now try increasing the FM fre(l~len<:y cleviat,ion so t,llat t l ~ eloop l~reakslock. Not,e t,lle response a t t l ~ e phase cornparat,or o ~ ~ t ancl p ~ YCO ~ t input,. 2.2 XOR Phase Detector tvklat happens if you s ~ ~ t ) s t , i tphase ~ ~ t e <:ornparator I (an ex<:l~~sive-or gate) for phase cornparator I1 in t l ~ e lag cornpensaterl PLL (ies<:ril~e(i l)e a l ~ l et,o arlswer this clllestion t,lleoretically arlrl in Part 2.1Y Y ~ I sho~llcl I experimentally. S~~ecifi<:ally, what is t,lle phase (iet,ector gair~I l o . t l ~ eloop l~anrlmirlt,h,t,lle phase margin, t l ~ e st,ea(iy stat,e phase error. t l ~ elock range. and t,lle ease of a ~ : ( l ~ ~ i rlock i n g (ex~~erirr~entallj~)? Note: if yo^^ llave rliffic~llt,yin a c q ~ ~ i r i nlock, g t,ry slowly scarlrlir~gthe input fre(l~len<:y llr~tilthe <:ir<:~~it locks. 11-ill this circuit lock on harrnoni<:s? Is the <:ircuit rluty c:yc:le sensit,ive'? 3 Active Filters Ret,urrl to t,lle lag cornpensaterl PLL ~ l s i r ~phase g cornparator I1 as in Part 2.1. Apply a FM rno(illlater1 input t,o ol)serve t l ~ est,ep response as t)efore. Look a t t l ~ eo ~ ~ t ofp t~l ~ ephase t <:ornparator (pi11 13). The st,ea(iy st,ate phase error and dynamic trackir~gerror sho111(il)e apparent if you rnentally average ant the high freclllencjr c o r r ~ ~ ~ o n e nTry t s ~varying . range. t,lle i n p ~ freq~lency ~t .ict,ive filters are ~lserlto re(ill(:e illis t,racking error. .i possil)le active filt,er PLL realizat,ior~is illl~st,raterl in Figure 1. Figure 4: .ict,ive 10011 filter Certair~preca~~tions rrlllst t)e taker^ when sll<:hfilters are I I S P ~The . oparnp car1 easily s ~ ~ p p voltages ly t . illis reason. it is a goorl irlea. to rliode clarnp t,lle i n p ~ ~to t s t l ~ ePLL t,o the 1016 illat mill 11llr11it o ~ ~For W~i,tr: If you tind mrntsl averaging nnssaisfying. filtrring 1." with s simplr passive R(: filaer with R(: = 0.1 ms will give pic611re uf t h a~verage value of ahr phasr rrnlr. Tu avoid lrvsding the phase <:ompsrsai,rwith a lini imprdsncr. make ahr rrsisair R s largr viihlr (lh112 is tin?). Ih1PORT.&NT: this filaer is not in thr li~op.it is hrtiirrll thr phasr <:ompsrsai,ronapnr and thr sl.i,rrr. )7111 B Cite as: James Roberge, course materials for 6.302 Feedback Systems, Spring 2007. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY]. as shox3-n. The low pass filt,er (R:3 r111d C2) provides extra r%tt,e~~llat,inr~ nf t,l~ehigh freql~encyphase rletector ripple. It also shol~l(ikeep t,lx oparr~pfrorr~slew rat,e lirnit,ing. Again the act,ive circuit sl~ecifiest,lx open state out,pl~tof phase cletect,nr I1 t,n 1)e 2.5 vnlts. The ir~verter is necessary 1)ecallse the PLL wants a non-inverting topology. R ~ C Iset,^ the (:rnssnver fre(lller~<:y,& I I ( ~Rz sets t,lx zero locat,ion. l ~ e r ~ ct,lx e stal~ility. 1/(R:3C2) sl~olllrll ~ eset at least a fact,or of S al~ovew,. I l o is t,he sr1111e as l~efore(as it rnol~l(il ~ for e any loop filter r r l ~ i c lsl~ecifiecl ~ t,lx open st,ate volatage of the phase clet,e<:toras 2.: volts). Feel free to rlesign your own seconcl orrler loop filter t,opology if y o l ~wish, just l ~ carefill e rlot t,o clestroy t,l~e1016. Design ancl t)llilrl a. PLL llsirlg an a<:ti\.e loop filt,er t,o rrleet t l ~ efolorrir~gspecifi<:ations: loop c:rossover freclllency phase rr~argir~ center frecll~ency lock range st,eacly stat,e error p11ase (iet,ec:tnr w, = $, fi, 1000 rarl/s = 15" = 19 kHz 18 kHz to 20 kHz e,, = 0 I1 Draw t,lx appropriat,e Dorle ~ ~ l o t , Make s. rrleasllrerrlerlts of t,lx step response. Again look at t,l~ephase l t e t I ( I 13). 11-hat car1 you say a l ~ o l t~lt~ erlyr~arr~ic tracking error'! 11-hat at)out t,he steady st,at,e error? 4 Frequency Limitations Deterrr~ir~e the r r ~ a x i ~ r ~nperr~tir~g ~ l r r ~ freclller~cynf t l ~ ePLL. It may l)e cor~ver~ier~t to use a sirr~plepassive loop filter wit11 a fairly mirle loop l)ancl\3-iclth (d, = 10 krps). Is the ir~r%xirr~~~rr~ fre(l~~er~(:y greater f ~ Phase r Cornparat,or I or II'! W ~ a ist t l ~ elirr~itir~g fr~ctor,t,l~eYCO or the phase <:ornparator? Cite as: James Roberge, course materials for 6.302 Feedback Systems, Spring 2007. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].