Realization of Nuclear Fusion Fast Control Plant Computing Architecture

advertisement

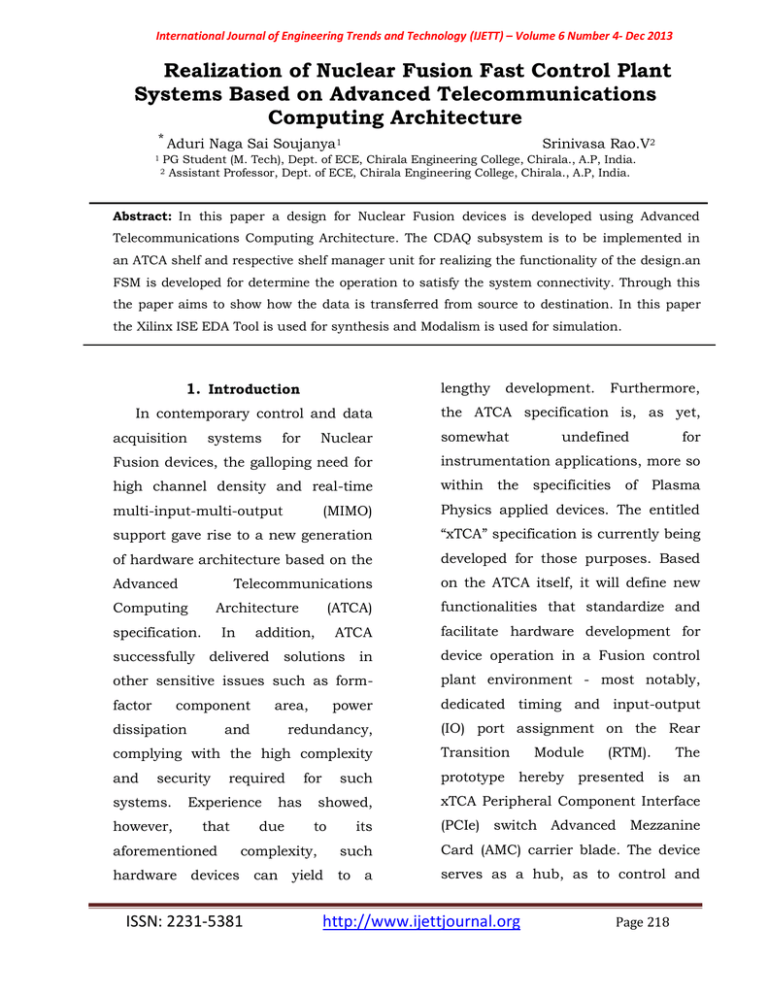

International Journal of Engineering Trends and Technology (IJETT) – Volume 6 Number 4- Dec 2013 Realization of Nuclear Fusion Fast Control Plant Systems Based on Advanced Telecommunications Computing Architecture * Aduri Naga Sai Soujanya1 1 Srinivasa Rao.V2 PG Student (M. Tech), Dept. of ECE, Chirala Engineering College, Chirala., A.P, India. Assistant Professor, Dept. of ECE, Chirala Engineering College, Chirala., A.P, India. 2 Abstract: In this paper a design for Nuclear Fusion devices is developed using Advanced Telecommunications Computing Architecture. The CDAQ subsystem is to be implemented in an ATCA shelf and respective shelf manager unit for realizing the functionality of the design.an FSM is developed for determine the operation to satisfy the system connectivity. Through this the paper aims to show how the data is transferred from source to destination. In this paper the Xilinx ISE EDA Tool is used for synthesis and Modalism is used for simulation. lengthy 1. Introduction In contemporary control and data acquisition systems for Nuclear development. Furthermore, the ATCA specification is, as yet, somewhat undefined for Fusion devices, the galloping need for instrumentation applications, more so high channel density and real-time within multi-input-multi-output (MIMO) Physics applied devices. The entitled support gave rise to a new generation ―xTCA‖ specification is currently being of hardware architecture based on the developed for those purposes. Based Advanced on the ATCA itself, it will define new Telecommunications Computing Architecture specification. In addition, the specificities of Plasma (ATCA) functionalities that standardize and ATCA facilitate hardware development for in device operation in a Fusion control other sensitive issues such as form- plant environment - most notably, factor power dedicated timing and input-output redundancy, (IO) port assignment on the Rear successfully delivered component dissipation solutions area, and complying with the high complexity Transition and prototype security systems. however, required Experience that aforementioned hardware for has due such showed, to complexity, devices ISSN: 2231-5381 can yield its Module hereby (RTM). presented The is an xTCA Peripheral Component Interface (PCIe) switch Advanced Mezzanine such Card (AMC) carrier blade. The device to serves as a hub, as to control and a http://www.ijettjournal.org Page 218 International Journal of Engineering Trends and Technology (IJETT) – Volume 6 Number 4- Dec 2013 handle I/O data from its parent nodes particles existing within the same xTCA shelf the existing through facilities, and its proprietary fabric and beyond in previous therefore radiation channels in dual-star topology. Parent effects node blades, under development, are be equally Commercial Off The Shelf (COTS) linked through xTCA's in radiation subsystems deeply agnostic fabric in full-mesh topology, components as radiation to attain system MIMO is no AMC of commercial grade to of but, reliability often alternative there to the use components and for a much more independent and their speedier hardware development, as managed. High reliability hard dedicated AMC modules, such as data components, primarily processing and storage devices, can for be market, projected. risk is modularity and versatility. This allows simultaneously the under a The switch blade carries up to four up Use operating concern adding to considered. functionality from all I/O endpoints. modules, have use associated has military are to to be developed and space expensive and Commercial off-t he-shelf (COTS) AMC functional products are readily available and limited. may also be immediately integrated in effects the system. Numerous international and testing on programs are forecasted/ underway is of relevance as radiation effects to explore energy physics, nuclear studies fusion have and fission and medical physics. Such large scale physics experiments degree demand of availability. performance the Mitigation for in high automation and availability is acquisition challenge IPFN. to development requirements (Reliability, for Availability, Maintainability, Inspect ability). Also, diagnostics for performance measurements be to subject ISSN: 2231-5381 high levels reliable a operation representative technologies systems of designed may The of tier high- and data an ongoing fosters the Advanced Instrumentation and Architecture fully for program High availability. follows methodology http://www.ijettjournal.org on is program Computing high program control Such Physics provided knowledge. research providing and control systems able fulfill radiation not yet a The of emerging exhaustive A more a multi- addressing Page 219 International Journal of Engineering Trends and Technology (IJETT) – Volume 6 Number 4- Dec 2013 the issues at the firmware, software/middleware; hardware the levels. ITER The is adopted system integrated R&D Architecture Computing (ATCA) to industry importance scenarios. prototype, based contributes board Fast (FPSC) prototyping ITER controller will requirements. acquisition complies System guidelines and be given projects a project innovative design ‐tolerant, for time safety control systems and used energy Advanced in physics Telecommunications Computing Architecture (ATCA or Advanced TCA) is the module largest ITER history with of critical experiments. ATCA limitations COTS based, For of tests in aware, characteristics. developed real on methodologies high IPFN most technologies. emphasis acquisition The foreseen develop of focusing also several as standard of and Details to the presented environment. applied with of the the on a integration into fast targeting connectivity the regarding family Plant the standardization, prototype, data on to on The data This modules in presents acquisition, new well as is benefits for a solutions the specialized the tested description which FPSC controller complete addressed, features plasma contribution, be contribution specifically this will operation effort In high and with discharges. results its systems duration relevant greater activity long control devices high to ATCA. fusion CODAC become an nuclear was (HA) This of ATCA availability steady state acquisition C&DA characteristics of and data the develop instrumentation. due to IPFN Advanced Telecommunications standard in program. PICMG‘s chosen of prototype controller this and availability specification of the effort PCI in the Industrial Controller Computer rear IO (PICMG), in companies participating. Known as for redundancy, Manufacturers with more Group than 100 order to provide high Advanced levels of reliability and specification designation PICMG 3.x ISSN: 2231-5381 http://www.ijettjournal.org TCA, the official Page 220 International Journal of Engineering Trends and Technology (IJETT) – Volume 6 Number 4- Dec 2013 was ratified by PICMG the back plane. The IPMC sends an December IPMI event message to the Shelf targeted Manager to let it know that it has primarily to requirements for the next been installed. The Shelf Manager generation grade" reads information from the blade and communications equipment, but has determines if there is enough power recently expanded its reach into more available. ruggedized applications geared toward Manager sends a command to the the mil/aero industries as well. This IPMC to power-up the payload part of series of specifications incorporates the blade. The Shelf Manager also the speed determines next- supported by the blade. It then looks generation processors, and improved at the fabric interconnect information Reliability, for the backplane to find out what organization the in 2002.AdvancedTCA latest of "carrier trends interconnect is in high technologies, Availability and Serviceability (RAS). If there what is, the fabric Shelf ports are fabric ports are on the other end of the fabric connections. If the fabric ports on both ends of the backplane wires match then it sends an IPMI command to both blades to enable the matching ports. Once the blade is powered-up and connected to the fabrics the Shelf Manager listens for event messages from the sensors on the blade. If a temperature sensor reports that it is Figure 1 14-slot ATCA shelf too warm then the Shelf Manager will Blades (boards) increase the speed of the fans. AdvancedTCA blades can be Processors, Switches, AMC carriers, etc. A typical shelf will contain one or more switch blades and several processor blades. shelf the FRU data in the board contains descriptive information like the manufacturer, model number, serial number, manufacturing date, revision, etc. This information can be When they are first inserted into the The onboard IPMC is read remotely to perform an inventory of the blades in a shelf. powered from the redundant -48V on ISSN: 2231-5381 http://www.ijettjournal.org Page 221 International Journal of Engineering Trends and Technology (IJETT) – Volume 6 Number 4- Dec 2013 (EET) signals 2. Working Principle The CDAQ subsystem is to be messages deterministic timing (sequence of words) implemented in an ATCA shelf and modulated on a carrier clock, which respective shelf manager unit. The carry trigger/event signals transport, typical capacity of an ATCA shelf is of clock 14 boards (blades), located in slots. stamp] [11]. The T&S redundant hub Slots are hereby named by their is to be installed on slots 3 and 4 and logical The distributes these signals to the node- communications networks presented blade slots (5 to 14), forming the in this section make use of all peer-to- respective peer (P2P) links available on ATCA‘s Serial gigabit protocols such as SRIO, fabric interface backplane, grouped in Aurora, may be setup to establish this three fabrics: one PCIe, in dual-star, network on the ATCA agnostic fabric. and two SRIO, in full-mesh and dual- The star network, represented on the right side of Fig. 2. illustrated on the left side of Fig. 1, is The other network implemented on controlled by two redundant PCIe- the fabric interface connects all nodes hubs on (logical) slots 1 and 2, each (slots 5 to 14) in full-mesh topology one connecting to the remaining slots and is depicted in Fig. 3. The protocol (3 to 14) through the appropriate used for data fabric channels, forming a PCIe dual- any of the same range of choices as in star[11]. This redundant PCIe-hub set the is responsible for handling IO data allows, in conjunction with the PCIe from all endpoints located on every and parent blade (Nodes and T&S hubs) subsystem to achieve real-time MIMO and on the PCIe-hubs themselves. connectivity to every endpoint [11]. slot subsets. numbers. The PCIe skew correction, fabric redundant T&S T&S and dual-star T&S time subset. network transfer may also be network. networks, This the network CDAQ The second network to be established aims to distribute a customized group of timing and synchronization signals. These may be Binary State Timing (BST) signals (clock, trigger, and gate type signals), Multiplexed BST (mBST) signals (synchronous time Figure 2 Redundant T&S network multiplexed BST signals on an n-bit word), and Encoded Event and Timing ISSN: 2231-5381 http://www.ijettjournal.org is Page 222 International Journal of Engineering Trends and Technology (IJETT) – Volume 6 Number 4- Dec 2013 PCIe-Hub: The PCIe-hub is the main module of the CDAQ subsystem. It can be said that this device builds the hardware design foundations for the other two. The switching is provided by a PEX 8696 which offers 96 PCIe Gen 2 (5 GT/s) ages, capable of configuring up to 24 flexible ports, up to 8 upstream ports for Figure 3 Full-Mesh Topology As an example, there is an element marked on column 6/row 7, which corresponds to slot 6/channel 7. To see where slot 6/channel 7 connects, we must read the element (8–6), which corresponds to slot 8/channel 6 [11]. The three types of hardware modules here discussed are quad AMC (mid or full-size) carrier blades. In addition, the TCA workgroup is developing ATCA that others, RTM synchronization will define, among timing PICMG and xTCA for Physics IO, Timing and Synchronization Technical Committee) [1], E-Keying and hardware management support (IRTM) [1]. While these works are still under progress, the compatibility goal with is to the create AMC specification so that an RTM will be managed similarly to the AMC by the overall system‘s hardware management platform. ISSN: 2231-5381 applications, on-chip Non- transparent port for dual-host and fail-over applications support. It is this and unit hot-plug that, in redundant operation, on logical slots 1 and 2, implements the PCIe dual-star network, connecting links to every ATCA fabric channel. The PEX 8696 3. Hardware Modules extensions backplane also switches each AMC module (links) and the RTM (and links). The PCIe reference clock REFCLK) signal is spread over the backplane through the ATCA‘s clock synchronization interface on ATCA LK3, which is a user-defined signal. AMC‘s corresponding signal is FCLKA. Again, the PICMG xTCA for Physics IO, Timing and Synchronization Technical Committee is carrying out a standardization of all clock signals within ATCA, MC, and RTM so that they can be compatible to every FRU and through the backplane. Following these directives, irtex-6 LXT Field Programmable Gate Array (FPGA) was chosen to implement this distribution scheme, for it delivers the necessary IO http://www.ijettjournal.org Page 223 International Journal of Engineering Trends and Technology (IJETT) – Volume 6 Number 4- Dec 2013 and logical resources (128 000 logic T&S-hubs is to be located on logical cells, a maximum of 600 user IO ports slots 3 and 4 and form a dual-star T&S and 20 6.6 Gb/s TX transceivers) to network to the nodes located from slots establish a cross point switch for all 5 to 14. The board‘s architecture is these signals. REFCLK, as well as all based on the ATCA/AMC/RTM lock signals, may the preceding section, and its main flow from any designated source to components are the same but some of every endpoint of the system. This the implementation is complemented y a components, the fabric interface, and de-jittering circuit that feeds the PEX the supported FRU‘s were changed. The 8696 and the Virtex-6 FPGA PCIe PEX 8696 switches all REFCLK inputs. REFCLK may also be within the module, which are the same generated by a local crystal oscillator as on the PCIe-hub. However, the T&S- and input to the cross point switch. The hub is seen as a ―node‖ to the PCIe FPGA high-speed network, so only two PCIe ports link to connectivity to the PEX 8696 (PCIe ) the fabric interface, connecting to the and to each of the five FRUs (SRIO ) redundant PCIe-hub set, as discussed through its PCIe Gen 2 compliant GTX in the previous sections. The remaining transceivers. fabric also provides PCIe-hub, described in connections interface between PCIe connections its inks will establish the T&S dual-star, controlled by the Virtex-6 FPGA, which links the customized 4-lane set of T&S signals to each corresponding fabric channel port. Three lanes are reserved for HighSpeed LVDS BST signaling ( Gbit) (ANSI TIA/EIA-644 Standard) and the fourth lane dedicated to mBST or EET signaling. Thus, in addition to the clock Figure 4 PCIe Hub distribution functions, as performed on T&S-Hub the PCIe-hub, the Virtex-6 FPGA will The T&S-hub‘s main goal is to implement switching of the custom T&S generate and distribute a customizable signals to all set synchronization encoding/decoding for the EET timing signals to its parent Nodes through the signal. A complementary circuit will of timing and MC/RTM modules and ATCA backplane. A redundant set of ISSN: 2231-5381 http://www.ijettjournal.org Page 224 International Journal of Engineering Trends and Technology (IJETT) – Volume 6 Number 4- Dec 2013 provide local generation of the T&S Intelligent signals. Controller and Power Distribution All xTCA Platform main-board Management prototypes above described are required to implement an Intelligent Platform Management Controller (IPMC). Within a specific blade, nd its contained AMC and RTM units, the IPMC is the representative of the overall management hardware platform system, which provides the ability to manage power supplies, Figure 5 T&S Hub backplane interconnect resources, Node Blade event The node blade is the exact same programming, among others [7]. Each hardware of the T&S-hub. Both PEX IPMC communicates with the hardware 8696 port platform management system through assignments were planned so that is the Intelligent Platform Management possible different Interface (IPMI), implementing the local prototypes from only one PCB, the Intelligent Platform management Bus hardware role is defined y firmware (―IPMB-L‖). The device used is a core only. As there is a maximum of 10 (ten) IPM OPMA2368 [1], which provides slots for node blades (slots 5 to 14), the ATCA-compliant hardware management FPGA will now be configured to use its capability and features a wide set of IO connections to the upper nine fabric peripheral channels as P2P links to each sibling, Integrated Circuit [6], the protocol in so that all Nodes resent in the system which the IPMB is implemented. and to Virtex-6 develop FPGA‘s two monitoring, drivers, or device including Inter- form a full-mesh network. The lower FPGA fabric-channel links will receive T&S signaling to e spread to all of the Nodes‘ endpoints. ATCA/AMC/RTM Distribution clocks of is implemented in analogy with the PCIehub blade architecture, and PCIe connectivity in analogy with the T&Shub, making use of the PEX 8696. D. ISSN: 2231-5381 Figure 6 Pay load and Power Distribution Finally, distribution power also http://www.ijettjournal.org management have the and same Page 225 International Journal of Engineering Trends and Technology (IJETT) – Volume 6 Number 4- Dec 2013 implementation scheme for every blade processing, type. An TC250 high-density dual-input timing units, may be added to the system converter [2] generates on-board payload with and established system networks. management power from the ensured redundant pair of -48Vdc ATCA inputs. Different payload voltages required for all blade components are obtained from data storage devices, connectivity to or the 4. Results & Conclusions An architecture solution for fast control plant systems was presented. It adequate dc-dc converters or voltage is based upon a development of regulators. The IPMC is required to ATCA specification, the most promising control architecture to substantially enhance individual payload and the management powers for each AMC (and the RTM) existing standard systems. The AMC- FRU. This is achieved using performance and capability of TPS2359 dual-slot AMC controllers [2]. carrier Fig. and modular, expandable CDAQ and favors management power distribution scheme. COTS integration. ATCA‘s upcoming E. User Applications There are many extensions provide diverse IO solutions possibilities on how to setup the overall Being system, as each blade may carry any type currently available xTCA specifications, of this paper aims to offer a set of base 6 shows compatible these, on the the payload AMC/RTM node modules. blades will be format designed provides according prototypes which can perform flexible, to the highly preferably used for IO endpoints (ADC future CDAQ applications, in a Fusion and/or DAC). The node blades will then control plant environment. Fig 7 & 8 fake advantage of the established full- gives you the Simulation result and mesh RTL schematic of the Proposed Control network for MIMO control. Additionally, each node blade has the System. capacity utilization Summary. to perform (on its FPGA) Table-1 shows the Device functions like data pre-processing or event management. The user may then transfer the desired data, via the PCIe network, to the PCIe-hub, on to the PCIe host computer, which will be one of MC/RTM PCIe-hub modules. This is just one suggested system setup. According to the user‘s needs, other types of compatible AMC/RTM cards, as data ISSN: 2231-5381 Figure 7 Simulation Result for the Proposed system http://www.ijettjournal.org Page 226 International Journal of Engineering Trends and Technology (IJETT) – Volume 6 Number 4- Dec 2013 References: [1] D. F. Valcárcel et al., ―An ATCA embedded data acquisition and control system for the compass tokamak,‖ Fusion Eng. Design, vol. 84, no. 7-11, pp. 1901–1904, Jun. 2009. Figure 8 RTL SCHEMATIC of the Proposed System Table-1 Device Utilization Summary Logic Utilization Used Available Utilization Number of Slices containing only related logic 0 0 0% Number of Slices containing unrelated logic 0 0 0% Number of bonded IOBs 77 804 9% IOB Flip Flops 3 Number of GCLKs 1 4 25% Number of GCLKIOBs 1 4 25% Total equivalent gate count for design 24 [2] A. J. N. Batista et al., ―ATCA control system hardware for the plasma vertical stabilization in the JET tokamak,‖ IEEE Trans. Nucl. Sci., vol. 57, no. 2, pp. 583– 588, Apr. 2010. [3] PCI-SIG®. [Online]. Available: http://www.pcisig.com/specifications/ pciexpress/. [4] Volnei A. Pedroni, ‗Circuit Design with VHDL‘, MIT Press, England. [5] Charless H. Roth, Jr (2005) ‗Digital Systems Design Using VHDL‘, 3 rd edition, Thomson Asia private limited, Singapore. [6] Bhaskar .J (2004) ‗A VHDL Primer‘, 3rd Edition. [7] Additional JTAG gate 3,744 count for IOBs PICMG® Mezzanine AMC.0 Card R2.0—Advanced Base Specification, PCIMG, 2006. SYNTHESIS REPORT [8] PICMG® 3.4 R1.0 specification—PCI Total 5.939ns (5.019ns logic, 0.920ns Express™ Advanced Switching for route) (84.5% logic, 15.5% route) Advanced TCA® Systems, PCIMG, 2003. Total memory usage - 252308 kilobytes [9] A. J. N. Batista, J. Sousa, and C. A. F. Varandas, Acknowledgements the ―ATCA digital controller hardware for vertical The authors would like to thank plasmas in tokamaks,‖ anonymous Instrum., vol. 77, p. 10F527, 2006. reviewers for their stabilization Rev. of Sci. comments which were very helpful in [10] improving the quality and presentation Coordinating Committee, 2009. [Online]. of this paper. Available: http://www.picmg.org/pdf/ ISSN: 2231-5381 PICMG http://www.ijettjournal.org xTCA for Physics Page 227 International Journal of Engineering Trends and Technology (IJETT) – Volume 6 Number 4- Dec 2013 PICMG_Physics_Public_Web_Update_061 209_R5-3.pdf. [11] Miguel Correia et.al, ―ATCA-Based Hardware for Control Acquisition on Nuclear Control Plant and Data Fusion Fast Systems‖, IEEE transactions on nuclear science, Vol. 58, No. 4, August 2011. Authors Profile: Aduri Naga Sai Soujanya is Pursuing her M. Tech from Chirala Engineering College, Chirala in the department of Electronics & Engineering (ECE) Communications with specialization in VLSI & Embedded systems. Srinivasa Rao. V is working as an Assistant Professor in the Department of ECE in CEC Chirala. He has 5 years of Teaching Experience and 1 year Industrial Experience in various organizations ISSN: 2231-5381 http://www.ijettjournal.org Page 228