2 1 6 3

advertisement

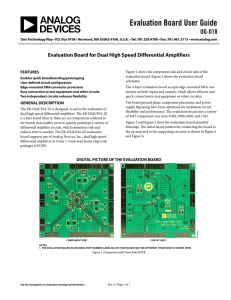

8 6 7 THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. 2 3 4 5 REVISIONS JUMPER TABLE REV JP# THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY ANALOG DEVICES. ON OFF 1 2 3 RELAY CONTROL CHART D 4 CONTROL CODE DEVICE FUNCTION 1 CONNECTOR DESCRIPTION DATE APPROVED A INITIAL RELEASE 02JUL12 D SMITH B CHANGE PER ECR-039386 07SEP12 D SMITH C CHANGE PER ECR-040288 07NOV12 D SMITH D CHANGE PER ECR-040670 04FEB13 D SMITH E CHANGE PER ECR-042286 10JUN13 N BENAMATI F CHANGE PER ECR-044221 04NOV13 D SMITH G CHANGE PER ECR-046414 29MAY14 M BEARDS D 5 * SEE ASSEMBLY INSTRUCTIONS C C B B TEMPLATE ENGINEER DATE HARDWARE SERVICES ------------ A N A LO G D EV C E S SCHEMATIC ------------ HW TYPE : EVAL Board Product(s): ADE7933 HARDWARE SYSTEMS -----------TEST ENGINEER ------------ A A COMPONENT ENGINEER -----------TEST PROCESS -----------HARDWARE RELEASE ------------ DESIGNER MASTER PROJECT TEMPLATE PTD ENGINEER UNLESS OTHERWISE SPECIFIED DIMENSIONS ARE IN INCHES M LABRANCHE TBD BK/BD SPEC. SOCKET OEM OEM PART# HANDLER DECIMALS X.XX +-0.010 X.XXX +-0.005 CHECKER D SMITH 8 7 6 5 4 TOLERANCES D SMITH P.O SPEC. TESTER TEMPLATE 3 FRACTIONS +-1/32 ANGLES +-2 2 REV. DRAWING NO. G 02-034694 SIZE DD SCALE CODE ID NO. 1:1 CodeID SHEET 1 1 OF 7 8 6 7 2 3 4 5 1 REVISIONS REV ADE7933 PHASE A ADE7978 DUT ZX/DREADYB_ADE XTALIN_ADE XTALOUT_ADE VT_A DATA_A VDD 1 IMIN V1OIN_A 1 V2PIN DATA V2PIN_A XTAL1 AGND_A VT_B DATA_B RESET_EN_N CLKOUT SYNC VT_C DATA_C C2 1 2 XTALIN_ADE WHT IPIN_B VDD_ADE 1 IPIN VDD GND MOSI/SDA MISO/HSD SCLK/SCL SS_N/HSA CF3/HSCLK 21 20 19 18 17 16 15 VDD_ADE MOSI/SDA_ADE MISO/HSD_ADE SCLK/SCL_ADE SSB/HSA_ADE CF3/HSCLK_ADE ADUC INTERFACE 0.1UF 4.7UF 10UF 0.1UF C34 C35 1G 8 9 10 11 12 13 14 3 D Q1 WHT 1 2 S C38 10UF C37 C PTC10DAAN CF3/HSCLK_ADE DNI K24A FDV302P CF3 1 1G 2 Q2 3D CF_1_ADE 0.1UF 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 S 3 D Q3 CF_2_ADE CF_3_ADE 1 IMIN V1PIN 1 C33 DNI B 10K C19 R40 DNI DNI SYNC VT_C SYNC V2/TEMPB AGND_ADC1 VDD_ADE 10K XTAL1 R9 V2PIN_C 10K DATA R29 1 VIOLET V2PIN RESET_ENB DATA_C CLK4M RESET_ENB 10UF ADE7933DUT V1PIN_C 0.1UF 1 RED CF2_B_ADE K24A FDV302P CF2 1 1G VDD_ADE DS6 1 A C LNJ208R8ARA (RED) DS5 IMIN_C S VDD_ADE VDD C IPIN FDV302P 2 VDD_ADE DNI A DS4 C CF1 C IPIN_C LNJ208R8ARA (RED) A ADE7933 PHASE C DNI K24A CF1_B_ADE BLU VDD_ADE CF3/HSCLK_ADE IRQ0B_ADE MISO/HSD_ADE RESETB_ADE CF_1_ADE CF_2_ADE CF_3_ADE 80.6 AGND_ADC1 1 SYNC VT_B SYNC V2/TEMPB VDD_ADE VDD_ADE R31 XTAL1 80.6 V2PIN_B R30 DATA 80.6 VIOLET 1 V2PIN ADE7933 PHASE C ISO GRN CF2_B_ADE CF1_B_ADE RESETB_ADE IRQ1B_ADE IRQ0B_ADE RESET_ENB DATA_B CLK4M RESET_ENB R2 ADE7933DUT AGND_B GND_C ZX/DREADYB_ADE MOSI/SDA_ADE IRQ1B_ADE SSB/HSA_ADE SCLK/SCL_ADE VDD AGND_B B P7 VT_N DATA_N KEEP C6 AND C7 CLOSE TO DUT PIN21 (VDD) KEEP C8 AND C9 CLOSE TO DUT PIN22 (LDO) LNJ208R8ARA (RED) GRN C32 ADE7978 V1PIN V1PIN_B GND_B C18 LDO_ADE IMIN 1 IMIN_B BLU C ADE7933 PHASE B B 1 RED ADE7933 PHASE B ISO VDD_ADE D 20PF VT_N DATA_N IRQ0_N IRQ1_N RESET_N CF1 CF2 AGND_A 1 2 3 4 5 6 7 VT_B DATA_B RESET_ENB CLK4M SYNC VT_C DATA_C SYNC VT_A SYNC V2/TEMPB AGND_ADC1 1 RESET_ENB DATA_A CLK4M RESET_ENB 20PF 16.384MEGHZ U10 PAD DATA_A VT_A ZX/DREADY_N XTALIN XTALOUT DGND LDO ADE7933DUT VIOLET BLU 1 V1PIN GND_A GRN LDO_ADE PAD 28 27 26 25 24 23 22 IPIN IMIN_A Y1 VDD_ADE 2 WHT IPIN_A APPROVED C1 1 2 XTALOUT_ADE A 1 RED D DATE XTAL CIRCUIT 1 ADE7933 PHASE A ISO DESCRIPTION AGND_C AGND_C PJ-002AH-SMT P R3 120OHM DL4001 1 S3 3 2 4 B3S1000 C36 1UF VDD_ADE D7VDD_ADE A C 10K DNI 2 N P 1 N 0.1UF 1 VIOLET C16 1 1 1 1 C14 GRN DNI1 RESET A RESETB_ADE C AGND_D DNI E2 D6 AGND_ADC1 A V2PIN_N OUT ADJ 1 DNI DL4001 GND_N V2PIN RESET_ENB RESET_ENB DATA_N DATA CLK4M XTAL1 C17 ADE7933DUT RED DNI 470UF V1PIN DGND1 1 BLK 12V 47UF BLU IMIN V1PIN_N A VDD_ADE VDD DNI +V1 IPIN IMIN_N LM1117MP-3.3/NOPB VR3 4 3 OUT1 2 DNI IN 0.1UF WHT IPIN_N DNI RED N 5_12_IN DNI C11 1 2 3 DNI ADE7933 PHASE N P2 ADE7933 PHASE N ISO SYNC VT_N SYNC V2/TEMPB AGND_D AN A LO G DE V CES THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, SCHEMATIC HW TYPE : EVAL Board Product(s): ADE7933 DESIGN VIEW REV DRAWING NO. <DESIGN_VIEW> G 02-034694 OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. PTD ENGINEER SIZE SCALE D SMITH D 1:1 THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY OWNED ANALOG DEVICES. 8 7 6 5 4 3 2 SHEET 1 2 OF 7 8 6 7 2 3 4 5 1 REVISIONS REV DNI R32 10K 0 0 DNI R12 R35 VSS PAD SDA PAD 24LC32A-I/MC R17 100K R10 R36 U9 8 VDD_SDP_ADE VCC 7 WP 6 SCL_SDP SCL 5 SDA_SDP 1 A0 2 A1 3 A2 4 EEPROM_A0 100K GND ADUC INTERFACE GND P1 USB_VBUS 3.3V SPI MOSI/SDA_SDP S4 1 2 3 MISO/HSD_SDP 5 MOSI AND HSD BOTH CONNECT TO THE SAME PIN ON THE MICRO MISO_SDP SCLK/HSCLK_SDP SCL_SDP 8 7 9 CF3/HSCLK_SDP 11 10 12 GND MOSI/HSD_SDP SDA_SDP 4 6 SCLK/SCL_SDP 2 P VDD_SDP_ADE 120OHM N DGND2 1 BLK 1 1 N 12V 0.1UF P OUT ADJ 1 E1 0.1UF RED C10 +V2 COM SELECT TP45 LM1117MP-3.3/NOPB VR1 4 3 OUT1 2 IN C6 GND 0 GND DNI RED VDD_SDP_ADE R34 C12 EEPROM_A0 DNI R11 VDD_SDP_ADE 470UF B ID EEPROM C8 IRQ0B_SDP ZX/DREADYB_SDP VDD_SDP_ADE D 47UF SSB/HSA_SDP 120 119 118 117 116 115 114 113 112 111 110 109 108 107 106 105 104 103 102 101 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 FX8-120S-SV(21) 1 C 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 R33 34 SSB/HSA_SDP DNI 35 0 36 MOSI/HSD_SDP 37 MISO_SDP 38 SCLK/HSCLK_SDP 39 40 SDA_SDP 41 SCL_SDP 42 IRQ1B_SDP 43 RESETB_SDP 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 FX8-120S-SV(21) 100K USB_VBUS APPROVED P8 100K P8 5V DATE THIS IS THE SDP INTERFACE BD THIS ADAPTS THE METROLOGY BD TO THE SDP AS AN EVAL BD SDP INTERFACE D DESCRIPTION GND GND GND GND GND SCLK AND HSCLK BOTH CONNECT TO THE SAME PIN ON THE MICO 1 2 3 4 5 6 CF_2_SDP 7 CF_3_SDP 8 GND RESETB_SDP 9 CF_1_SDP 10 IRQ0B_SDP 11 MISO/HSD_SDP 12 VDD_SDP_ADE 13 CF3/HSCLK_SDP 14 SCLK/SCL_SDP 15 VDD_SDP_ADE 16 IRQ1B_SDP 17 SSB/HSA_SDP 18 ZX/DREADYB_SDP 19 MOSI/SDA_SDP 20 SSW-110-02-G-D C SSB AND HSA BOTH CONNECT TO THE SAME PIN ON THE MICRO I2C MSS420004 LABEL PROTOCOL SELECTION NEAR SWITCH B A A AN A LO G DE V CES THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, SCHEMATIC HW TYPE : EVAL Board Product(s): ADE7933 DESIGN VIEW REV DRAWING NO. <DESIGN_VIEW> G 02-034694 OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. PTD ENGINEER SIZE SCALE D SMITH D 1:1 THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY OWNED ANALOG DEVICES. 8 7 6 5 4 3 2 SHEET 1 3 OF 7 8 6 7 2 3 4 5 SECONDARY(ISO)SIDE 1 REVISIONS PRIMARY SIDE REV DESCRIPTION DATE APPROVED ANALOG INPUT PER PHASE IPIN IN D D E1_A IMIN IN IPIN R15_A R4_A 1K 0 DNI C16_A AGND_ADC 150OHM E3_A IN IMIN .033UF IN C IP TS4148 RZ E2_A AGND_ADC1 D3_A A C C15_A 150OHM TS4148 RZ .033UF IN D6_A DNI A R16_A R8_A 1K 0 IM 150OHM VDD R3_A OUT VDD 0 R22_A 10K E4_A R1_A R5_A R10_A R17_A 330K 330K 330K 0 V1P AGND_ADC1 VDDISO AGND_ADC V2P V1P AD4_AC AGND_ADC D1_A .033UF A C IN DNI 150OHM C11_A V1PIN 1K VM IM DNI IP TS4148 RZ LDO TS4148 RZ DNI D9_A A C IN D7_A A C C R14_A IN REF DNI TS4148 RZ TS4148 RZ 1 2 3 4 5 6 7 8 9 10 VDDISO GNDISO V2P V1P VM IM IP LDO REF GNDISO PULL_HIGH V2/TEMPB RESET_ENB DATA TS4148 RZ R2_A R6_A R11_A 330K 330K 330K OUT DATA OUT XTAL1 OUT GND SYNC ADE7933ARIZ OUT C2_A 0.1UF C1_A 10UF SUPPLY BYPASS TS4148 RZ LAYOUT NOTE: KEEP THE VDD BYPASS CAP CLOSE TO DUT PIN19 NOTE:KEEP THE HIGH FREQ BYPASS CAP(0.1UF) CLOSE TO THE DUT PIN DNI TS4148 RZ V2P B .033UF C10_A 1K NOTE: C19_X FOR SOLDERED DOWN VERSION ONLY R13_A 150OHM C RESET_ENB DNI IN B 10K R19_A 10K XTAL1 SYNC 1 2 D2_A A C DNI TS4148 RZ E5_A V2PIN D8_A A C DNI 0 D10_A A C R7_A D5_A A C AGND_ADC OUT .033UF C9_A 1K R12_A V2PIN V2/TEMPB R23_A AGND_ADC VM IN U1_A 20 GND 19 VDD 18 EMI_CTRL 17 V2/TEMP_N 16 RESET_EN_N 15 DATA 14 XTAL2 13 XTAL1 12 SYNC 11 1 2 V1PIN SUPPLY BYPASS A CLOSE TO PIN 1 CLOSE TO PIN 8 VDDISO C3_A 10UF C4_A 0.1UF AGND_ADC CLOSE TO PIN 9 REF LDO C5_A 4.7UF 2 1 LAYOUT NOTE: KEEP THE R9 0OHM RES CLOSEST TO PIN 10 AGND_ADC C13_A 4.7UF C6_A 0.1UF A C14_A 0.1UF AN A LO G DE V CES AGND_ADC LAYOUT NOTE: 1. KEEP THE BYPASS CAP CIRCUITS CLOSE TO THE DUT PINS IN THE FOLLOWING ORDER A.) REF B)LDO C.)VDDISO AND WITH HIGH FREQ. CAPS(0.1UF) CLOSEST 2. C11, C15 AND C18 FOR SOLDERED DOWN VERSION. AGND_ADC THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, 7 6 5 HW TYPE : EVAL Board Product(s): ADE7933 DESIGN VIEW REV DRAWING NO. <DESIGN_VIEW> G 02-034694 OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. PTD ENGINEER SIZE SCALE D SMITH D 1:1 THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY OWNED ANALOG DEVICES. 8 SCHEMATIC 4 3 2 SHEET 1 4 OF 7 8 6 7 2 3 4 5 SECONDARY(ISO)SIDE 1 REVISIONS PRIMARY SIDE REV DESCRIPTION DATE APPROVED ANALOG INPUT PER PHASE IPIN IN D D E1_B IMIN IN IPIN R15_B R4_B 1K 0 DNI C16_B AGND_ADC 150OHM E3_B IN IMIN .033UF IN C IP TS4148 RZ E2_B AGND_ADC1 D3_B A C C15_B 150OHM TS4148 RZ .033UF IN D6_B DNI A R16_B R8_B 1K 0 IM 150OHM VDD R3_B OUT VDD 0 R22_B 10K E4_B R1_B R5_B R10_B R17_B 330K 330K 330K 0 V1P AGND_ADC1 VDDISO AGND_ADC V2P V1P AD4_BC AGND_ADC D1_B .033UF A C IN DNI 150OHM C11_B V1PIN 1K VM IM DNI IP TS4148 RZ LDO TS4148 RZ DNI D9_B A C IN D7_B A C C R14_B IN REF DNI TS4148 RZ TS4148 RZ 1 2 3 4 5 6 7 8 9 10 VDDISO GNDISO V2P V1P VM IM IP LDO REF GNDISO PULL_HIGH V2/TEMPB RESET_ENB DATA TS4148 RZ R2_B R6_B R11_B 330K 330K 330K OUT DATA OUT XTAL1 OUT GND SYNC ADE7933ARIZ OUT C2_B 0.1UF C1_B 10UF SUPPLY BYPASS TS4148 RZ LAYOUT NOTE: KEEP THE VDD BYPASS CAP CLOSE TO DUT PIN19 NOTE:KEEP THE HIGH FREQ BYPASS CAP(0.1UF) CLOSE TO THE DUT PIN DNI TS4148 RZ V2P B .033UF C10_B 1K NOTE: C19_X FOR SOLDERED DOWN VERSION ONLY R13_B 150OHM C RESET_ENB DNI IN B 10K R19_B 10K XTAL1 SYNC 1 2 D2_B A C DNI TS4148 RZ E5_B V2PIN D8_B A C DNI 0 D10_B A C R7_B D5_B A C AGND_ADC OUT .033UF C9_B 1K R12_B V2PIN V2/TEMPB R23_B AGND_ADC VM IN U1_B 20 GND 19 VDD 18 EMI_CTRL 17 V2/TEMP_N 16 RESET_EN_N 15 DATA 14 XTAL2 13 XTAL1 12 SYNC 11 1 2 V1PIN SUPPLY BYPASS A CLOSE TO PIN 1 CLOSE TO PIN 8 VDDISO C3_B 10UF C4_B 0.1UF AGND_ADC CLOSE TO PIN 9 REF LDO C5_B 4.7UF 2 1 LAYOUT NOTE: KEEP THE R9 0OHM RES CLOSEST TO PIN 10 AGND_ADC C13_B 4.7UF C6_B 0.1UF A C14_B 0.1UF AN A LO G DE V CES AGND_ADC LAYOUT NOTE: 1. KEEP THE BYPASS CAP CIRCUITS CLOSE TO THE DUT PINS IN THE FOLLOWING ORDER A.) REF B)LDO C.)VDDISO AND WITH HIGH FREQ. CAPS(0.1UF) CLOSEST 2. C11, C15 AND C18 FOR SOLDERED DOWN VERSION. AGND_ADC THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, 7 6 5 HW TYPE : EVAL Board Product(s): ADE7933 DESIGN VIEW REV DRAWING NO. <DESIGN_VIEW> G 02-034694 OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. PTD ENGINEER SIZE SCALE D SMITH D 1:1 THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY OWNED ANALOG DEVICES. 8 SCHEMATIC 4 3 2 SHEET 1 5 OF 7 8 6 7 2 3 4 5 SECONDARY(ISO)SIDE 1 REVISIONS PRIMARY SIDE REV DESCRIPTION DATE APPROVED ANALOG INPUT PER PHASE IPIN IN D D E1_C IMIN IN IPIN R15_C R4_C 1K 0 DNI C16_C AGND_ADC 150OHM E3_C IN IMIN .033UF IN C IP TS4148 RZ E2_C AGND_ADC1 D3_C A C C15_C 150OHM TS4148 RZ .033UF IN D6_C DNI A R16_C R8_C 1K 0 IM 150OHM VDD R3_C OUT VDD 0 R22_C 10K E4_C R1_C R5_C R10_C R17_C 330K 330K 330K 0 V1P AGND_ADC1 VDDISO AGND_ADC V2P V1P AD4_CC AGND_ADC D1_C .033UF A C IN DNI 150OHM C11_C V1PIN 1K VM IM DNI IP TS4148 RZ LDO TS4148 RZ DNI D9_C A C IN D7_C A C C R14_C IN REF DNI TS4148 RZ TS4148 RZ 1 2 3 4 5 6 7 8 9 10 VDDISO GNDISO V2P V1P VM IM IP LDO REF GNDISO PULL_HIGH V2/TEMPB RESET_ENB DATA TS4148 RZ R2_C R6_C R11_C 330K 330K 330K OUT DATA OUT XTAL1 OUT GND SYNC ADE7933ARIZ OUT C2_C 0.1UF C1_C 10UF SUPPLY BYPASS TS4148 RZ LAYOUT NOTE: KEEP THE VDD BYPASS CAP CLOSE TO DUT PIN19 NOTE:KEEP THE HIGH FREQ BYPASS CAP(0.1UF) CLOSE TO THE DUT PIN DNI TS4148 RZ V2P B .033UF C10_C 1K NOTE: C19_X FOR SOLDERED DOWN VERSION ONLY R13_C 150OHM C RESET_ENB DNI IN B 10K R19_C 10K XTAL1 SYNC 1 2 D2_C A C DNI TS4148 RZ E5_C V2PIN D8_C A C DNI 0 D10_C A C R7_C D5_C A C AGND_ADC OUT .033UF C9_C 1K R12_C V2PIN V2/TEMPB R23_C AGND_ADC VM IN U1_C 20 GND 19 VDD 18 EMI_CTRL 17 V2/TEMP_N 16 RESET_EN_N 15 DATA 14 XTAL2 13 XTAL1 12 SYNC 11 1 2 V1PIN SUPPLY BYPASS A CLOSE TO PIN 1 CLOSE TO PIN 8 VDDISO C3_C 10UF C4_C 0.1UF AGND_ADC CLOSE TO PIN 9 REF LDO C5_C 4.7UF 2 1 LAYOUT NOTE: KEEP THE R9 0OHM RES CLOSEST TO PIN 10 AGND_ADC C13_C 4.7UF C6_C 0.1UF A C14_C 0.1UF AN A LO G DE V CES AGND_ADC LAYOUT NOTE: 1. KEEP THE BYPASS CAP CIRCUITS CLOSE TO THE DUT PINS IN THE FOLLOWING ORDER A.) REF B)LDO C.)VDDISO AND WITH HIGH FREQ. CAPS(0.1UF) CLOSEST 2. C11, C15 AND C18 FOR SOLDERED DOWN VERSION. AGND_ADC THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, 7 6 5 HW TYPE : EVAL Board Product(s): ADE7933 DESIGN VIEW REV DRAWING NO. <DESIGN_VIEW> G 02-034694 OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. PTD ENGINEER SIZE SCALE D SMITH D 1:1 THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY OWNED ANALOG DEVICES. 8 SCHEMATIC 4 3 2 SHEET 1 6 OF 7 8 6 7 2 3 4 5 SECONDARY(ISO)SIDE 1 REVISIONS PRIMARY SIDE REV DESCRIPTION DATE APPROVED ANALOG INPUT PER PHASE IPIN IN D D E1_N IMIN IN IPIN R15_N R4_N 1K 0 DNI C16_N AGND_ADC 150OHM E3_N IN IMIN .033UF IN C IP TS4148 RZ E2_N AGND_ADC1 D3_N A C C15_N 150OHM TS4148 RZ .033UF IN D6_N DNI A R16_N R8_N 1K 0 IM 150OHM VDD R3_N OUT VDD 0 R22_N 10K E4_N R1_N R5_N R10_N R17_N 330K 330K 330K 0 V1P AGND_ADC1 VDDISO AGND_ADC V2P V1P AD4_NC AGND_ADC D1_N .033UF A C IN DNI 150OHM C11_N V1PIN 1K VM IM DNI IP TS4148 RZ LDO TS4148 RZ DNI D9_N A C IN D7_N A C C R14_N IN REF DNI TS4148 RZ TS4148 RZ 1 2 3 4 5 6 7 8 9 10 VDDISO GNDISO V2P V1P VM IM IP LDO REF GNDISO PULL_HIGH V2/TEMPB RESET_ENB DATA TS4148 RZ R2_N R6_N R11_N 330K 330K 330K OUT DATA OUT XTAL1 OUT GND SYNC ADE7933ARIZ OUT C2_N 0.1UF C1_N 10UF SUPPLY BYPASS TS4148 RZ LAYOUT NOTE: KEEP THE VDD BYPASS CAP CLOSE TO DUT PIN19 NOTE:KEEP THE HIGH FREQ BYPASS CAP(0.1UF) CLOSE TO THE DUT PIN DNI TS4148 RZ V2P B .033UF C10_N 1K NOTE: C19_X FOR SOLDERED DOWN VERSION ONLY R13_N 150OHM C RESET_ENB DNI IN B 10K R19_N 10K XTAL1 SYNC 1 2 D2_N A C DNI TS4148 RZ E5_N V2PIN D8_N A C DNI 0 D10_N A C R7_N D5_N A C AGND_ADC OUT .033UF C9_N 1K R12_N V2PIN V2/TEMPB R23_N AGND_ADC VM IN U1_N 20 GND 19 VDD 18 EMI_CTRL 17 V2/TEMP_N 16 RESET_EN_N 15 DATA 14 XTAL2 13 XTAL1 12 SYNC 11 1 2 V1PIN SUPPLY BYPASS A CLOSE TO PIN 1 CLOSE TO PIN 8 VDDISO C3_N 10UF C4_N 0.1UF AGND_ADC CLOSE TO PIN 9 REF LDO C5_N 4.7UF 2 1 LAYOUT NOTE: KEEP THE R9 0OHM RES CLOSEST TO PIN 10 AGND_ADC C13_N 4.7UF C6_N 0.1UF A C14_N 0.1UF AN A LO G DE V CES AGND_ADC LAYOUT NOTE: 1. KEEP THE BYPASS CAP CIRCUITS CLOSE TO THE DUT PINS IN THE FOLLOWING ORDER A.) REF B)LDO C.)VDDISO AND WITH HIGH FREQ. CAPS(0.1UF) CLOSEST 2. C11, C15 AND C18 FOR SOLDERED DOWN VERSION. AGND_ADC THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, 7 6 5 HW TYPE : EVAL Board Product(s): ADE7933 DESIGN VIEW REV DRAWING NO. <DESIGN_VIEW> G 02-034694 OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. PTD ENGINEER SIZE SCALE D SMITH D 1:1 THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY OWNED ANALOG DEVICES. 8 SCHEMATIC 4 3 2 SHEET 1 7 OF 7