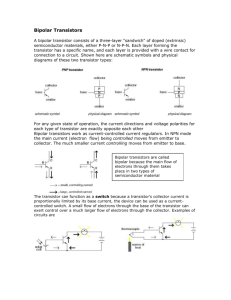

Vertical Profile Engineering and Reliability ... of Silicon-Germanium Heterojunction Bipolar Transistors

advertisement