Lab 6: Arithmetic Unit

advertisement

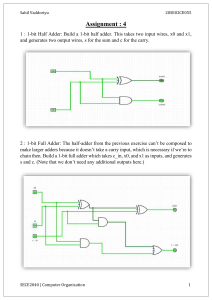

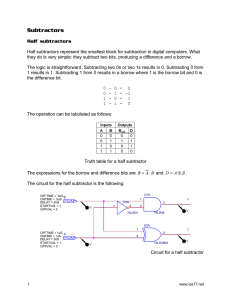

Lab 6 Digital Systems Laboratory ECE230L – Spring 2011 Lab 6: Arithmetic Unit Objective: Design, build, and test an adder/subtractor unit Lab Details: In class lecture, you have been shown how to build a larger functional unit using a basic module (with functionality verified). In this lab, you will apply a similar process to build an arithmetic unit with add and subtract functions. This arithmetic unit is to be controlled using just one control bit. Let’s call this control signal add /sub . When add /sub is 0, the arithmetic unit will add. Otherwise, it will function as a subtractor. Use of the arithmetic units in the Xilinx ISE libraries are not allowed. Tasks: 1. Pre-lab: Create a document with test values needed for Task 5 and bring to lab. Check-off: ________________ 2. Design a full-adder for addition of two 1-bit numbers. 3. Now using your design in (1), design an adder that adds two 4-bit numbers. Your design has to be modularized with hierarchy. 4. Modify your 4-bit-adder to function as a subtractor. 5. Use Xilinx ISE and simulator to verify your 1-bit and 4-bit designs. Choose a set of test values that test all scenarios including overflow conditions. This should cover all possible cases for carry-in and carry-out of the most significant bit. You need the test cases for both addition and subtraction. Check-off: ________________ 6. Implement your design on the FPGA using eight switches to input two 4-bit test vectors and one push button as add /sub control signal. 7. Provide a set of test cases (both addition and subtraction) with expected results for the TA to use during check off. (+7) + (+2) (+9) 0111 + 0010 1001 c4 = 0 c3 = 1 Overflow Example test case Check-off: ________________ Report: Record all results including, but not limited to: 1-bit module, 4-bit module, prototyping platform used, schematic diagram, simulation waveform, results, and discussions) in your team report. Boise State University Electrical and Computer Engineering Department Page 1 of 2 Digital Systems Laboratory ECE230L – Spring 2011 Lab 6 Deliverables: Check-off: TA to check off your circuit by end of lab period (11:55 AM) Submission: Due by Midnight Thursday 3/10/2011 Email: To: ece230lreport@gmail.com cc: your team partner Subject: Lab6_TeamX report (X is your team no.) Attachment: Lab6_TeamX.zip (contents as listed below) Attachment: (must be zip format – no others accepted) Contents of zip file: 1. Report File: \Lab6_TeamX_Report.pdf Report Content (create in Word using template previously provided) 1. Team number, team member names, lab no. and name 2. The original and simplified Boolean expressions 3. The original and simplified truth table 4. Simplification technique(s) 5. Type and number of chips used 6. Schematic diagram 7. Simulation waveform 8. Results and reflections After report has been created in Word, create a pdf and then zip. Boise State University Electrical and Computer Engineering Department Page 2 of 2