Lab 4: 8-Bit Arithmetic Logic Unit (ALU)

advertisement

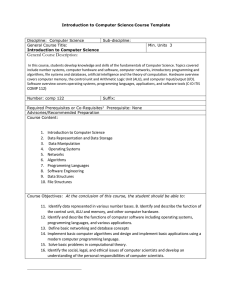

University of Florida Electrical & Computer Engineering EEL 4712 - Fall 2004 Revision 3 Lab 4: 8-Bit Arithmetic Logic Unit (ALU) Page 1/4 PURPOSE The purpose of this lab is to study the Arithmetic Logic Unit (ALU) with an Accumulator Register. This ALU will be used in later assignments. MATERIALS • • • • • Bin-Tek BT-U Board ByteBlaster Cable SPDT switch, 2 resistors Oscilloscope (in lab) Logic Analyzer (in lab) PRE-LAB REQUIREMENTS 1. Prepare a VHDL design file that describes a 1bit Arithmetic Logic Unit (ALU). The ALU supports the operations shown in the table below. A 3-bit input fsel selects the function to be performed. The 1-bit output of the ALU is f. The adder signals from the previous lab, a, b, cin, blk_g, and blk_p are also needed in the ALU. Some new inputs and outputs to support the shift functions are also needed. Use sli and sri as shift-left and shift-right inputs, respectively. The shift-left and shift-right outputs will be called slo and sro. The entity statement for our component should be called alu1. Your VHDL file should always begin with a comment containing your name and your section number as well as a canonical truth table that specify the values of all of the outputs relevant to that function as a function of all of the inputs. FSel 0 1 2 3 4 5 6 7 Dr. Eric M. Schwartz 8-Oct-04 FUNCTION Add with carry input (f = a + b + ci) Subtract (b-a) with borrow (f = /a + b + ci)* Bit-wise AND (f = a and b) Bit-wise OR (f = a or b) Bit-wise XOR (f = a xor b) Shift left (f = b << 1) Shift right (f = b >> 1) Zero (f = 0) * The ci for subtraction is the borrow input. The ALU may be conceptually viewed as shown in Figure 1. It is possible to implement this figure as a structural file using port map statements. If this approach is used, create separate VHDL behavioral descriptions of the multiplexers (of 2 different sizes). The multiplexers should be written using the VHDL “with...select” statement. These design files will be used together with the add1 file from Lab 3 to create the structural description of alu1. Compiling and testing proceeds as for other complex projects. Be sure to designate the project correctly -- use “Project | Set as Top Level Entity” to designate the top-level network as alu1. (A short-cut key sequence is Ctrl+Shift+J.) The VHDL architecture body may also be written in behavioral form using only assignment and with...select statements. Organize the file into sections separated by comments. Assume that there is a section for each function depicted in Figure 1. Note that the subtract function in Figure 1 is implemented by inverting the a input as it is sent into the adder. The AND, OR, and XOR functions have already been created in implementing the adder (remember the g, p, and the s outputs). The shift left and shift right operations can be implemented merely by rerouting the bus carrying the b input to the left or right one bit position. When all of the equations have been written for each section, build the multiplexer as shown at the bottom center of Figure 1 to select (based on fsel) the desired result. Notice that the adder and subtracter fit into this model as a single unit. Whether using the structural or behavioral VHDL description, name the project and assign the device appropriately. Compile and remove any errors until a suitable VHDL file is produced. Prepare suitable test vectors and simulate to verify that the output is identical to the truth table specified in the design. Please capture the test vectors in a .tbl file for use in the lab write-up. University of Florida Electrical & Computer Engineering Page 2/4 EEL 4712 - Fall 2004 Revision 3 Dr. Eric M. Schwartz 8-Oct-04 Lab 4: 8-Bit Arithmetic Logic Unit (ALU) Figure 1: 1-Bit Arithmetic Logic Unit 2. Prepare a logic diagram showing the structure of an 8-bit Arithmetic/Logic Unit (ALU) based on the alu1 component described above and the lca_gen component from Lab 3. Use text boxes to label the many external and internal signals. It is very important that all internal signals be labeled in order to support the following steps. The drawing is almost identical to the 8-bit LCA drawing from Lab 3. Suitable editing of a copy of the lab 3 design should result in a drawing for the 8-bit ALU with Look-Ahead Carry. Note the locations of the LCELLs that need to be embedded to retain the look-ahead carry structure. It is expected that the remaining signals within the alu1 network will be flattened (reducing the structure to single macrocells -one for f, one for sro, and one for sri). 3. Prepare a VHDL structural description of the 8bit Look-Ahead Carry ALU. To accomplish this step in an efficient manner, prepare a VHDL structural description of a 2-bit ALU with LookAhead Carry (alu2). This will involve 2 major components (alu1 and lca_gen) and the LCELL to preserve the internal signals associated with the Look-Ahead Carry structure. Insert LCELL instances on the g and p signals at all levels in the VHDL description. According to the drawing of a 2-bit ALU, there should be two instances of the alu1, one instance of lca_gen, and 4 instances of LCELL. The next step after alu2 is tested, is to build a 4-bit wide ALU having the same structure (alu4). There will be two instances of alu2, one instance of lca_gen, and four instances of LCELL. A final iteration produces an 8-bit ALU (alu8). A truth table is too extensive for inclusion in the VHDL files for alu2, alu4, or alu8. However, do include the function table. Remember to include your name and section number as a comment. Place the component statements for the three components in the design file. 4. Compile each project (alu2, alu4 and alu8) in order from the bottom of the hierarchy to the top, eliminate errors, and simulate the design. Look at the equations in the “.eqn” to verify that the appropriate look-ahead carry adder, as part of the ALU, was actually produced. It should be noted that without using LCELL components, the internal signals would have been minimized out of the design and the adder would look significantly different. Write a set of test vectors for each hierarchy level that will verify that each of the internal signals changes when expected. A complete set of test vectors will not be used in this assignment. Short runs of the waveform over a region of interest would be most effective. Show that the internal carries produced by the lca_gen components in the design still work. A test vector that shows when each of these carries changes to 1 is also needed. University of Florida Electrical & Computer Engineering Page 3/4 EEL 4712 - Fall 2004 Dr. Eric M. Schwartz 8-Oct-04 Revision 3 Lab 4: 8-Bit Arithmetic Logic Unit (ALU) Provide several well-chosen test vectors that show that all of the functions for each ALU work. 5. Use the Timing Analyzer to get estimates of the propagation times for the various paths in the 8bit ALU design. With the help of the Waveform Editor, the equations in the report file, and the logic diagram for the 8-bit Look-Ahead Carry Adder based ALU, verify that the timings are consistent with the intended design. 6. Add four single-bit output signals to the 8-bit ALU. These signals, called flags, inform the user of various bits of information about the result produced by the ALU. rising edge of the clock and that the register will not be loaded if load_enable is false. 9. An accumulator is shown in Figure 2. Use the adapted ALU and the register created above to build the accumulator. Write a structural VHDL file containing the two components mentioned. Since q comes out of the design and is used inside, it should be declared as a buffer. After the design is compiled, examine the equations that are placed in flip-flops in the FPGA. Perform suitable tests to show that the accumulator works. We will need an estimate of its speed when it is tested in lab and when it is used in a more complex system. • C - Carry Flag (equal to Cout) • Z - Zero Flag (true when f = 0) • S - Sign Flag (the value of f7) • V- Overflow Flag (2’s-comp. overflow) The Overflow Flag is determined by comparing the carry into the most significant bit of the adder with the carry out of that bit. If the two carries are the same, then there is no overflow (V=0). If the carries are different, then there is a 2’s complement overflow (V=1). Provide a new component that contains the necessary inputs, outputs, and logic equations to generate the desired signals. Test the component separately to verify that it works in simulation. 7. Adapt the structural file of the 8-bit ALU to contain these new flag components. The port statement for the ALU will need to be enlarged to let C, V, Z, and S be visible. Repeat the tests used for the ALU in the steps above to verify that the ALU performs properly using the new outputs. 8. Design a component that behaves like an 8-bit register. This VHDL file will contain the first PROCESS block used in the course. The process block is used to contain an IF statement which is a sequential statement. Refer to Appendix A of the text for more information. Statements in a process block are executed sequentially (the same as for C or Java). The register should be synchronously loadable from its 8-bit input d, on the rising edge of the clock. Simulate the register design using a small number of well-chosen test vectors to show that the device performs as required. One sequence of vectors that is very important is to show that loading occurs on the Figure 2: Accumulator 10. Look at your 3701 notes to design and build a debounced switch using an SR latch, two resistors and a SPDT switch. An SR latch can be made out of two NAND gates or two NOR gates. University of Florida Electrical & Computer Engineering EEL 4712 - Fall 2004 Revision 3 Dr. Eric M. Schwartz 8-Oct-04 Lab 4: 8-Bit Arithmetic Logic Unit (ALU) 3. If the accumulator had been set up in lab using a IN-LAB PROCEDURE Page 4/4 1. Design a test fixture that allows the propagation time for the worst case signal path through the 8bit ALU to be measured. Using the Timing Analyzer on alu8 can identify this path. Measure the propagation time for changes at the input signal to this path. Compare the measured values with the values for the same path produced by the Timing Analyzer and your use of the Waveform Editor and Simulator. A table should be prepared that shows this value for the alu8, add8 (LCA), and add8ripple (with ripplecarry). Include this table in the lab report. 2. Construct the 8-bit accumulator in the FPGA. The accumulator contains the 8-bit ALU with flags and the 8-bit register. Design a test fixture that allows the accumulator circuit to be exercised. This means that all of the functions of the ALU should be tested in meaningful combinations with reasonable data. For example, to test the AND function, a number must be placed in the register from input a using the ALU. Another number that clearly shows the action of the AND function is then placed on input a. The clock of the register is pulsed while the AND function is selected in the ALU. A cautionary note is in order concerning the choice of clock source for the register. If the clock is pulsed more than once, then the accumulator will produce incorrect results for the test desired. The Prototyping board in the lab has at least one de-bounced push button that will put out a single pulse each time it is pushed. (These switches have been known to have some problems.) Alternatively (and probably preferably), you may want to Construct your own debounce circuit using the SPDT switch in your lab kit along with some resistors and an SR-latch. QUESTIONS 1. List the names of the inputs to the 8-bit ALU (with flag network) and mark the number of bits in each signal. How many test vectors would be needed to test the complete 8-bit ALU? 2. What is an efficient test to show that all of the inter-bit carries were correct in the 8-bit ALU? The point here is to identify one or more test vectors that show the inter-bit carries take on the proper ‘0’ or ‘1’. Where, in all of the test data, is this information presented? non-debounced switch for the clock input, how could the number of times that the clock was pulsed be determined? Hint: you will need to specify the inputs to the accumulator and then interpret the results. 4. The text, in Figure 5.27, shows a form of the port map statement that should not be used in EEL 4712. Contrast this form with the other form shown in lecture. Specifically deal with how to specify which signals the port map connects the component in each case, how unused connections are shown, and justify why one or the other form is more likely to contribute to error-free coding. 5. We have built a subtraction network by exploiting the features of number representation. What feature did we exploit to replace the subtracter with an adder? What feature of what number system did we exploit to justify the network hooked to the a input of the FullAdder component in Figure 1? When we do subtraction with the alu8 network, we obviously apply 8-bit numbers to inputs a and b and set the input fsel = 1. If a = 0x15 and b= 0x9f, what are the values of all inputs needed to compute f = a - b? What are the values of produced on f and each of the flags? 6. Consider the shift network in the 8-bit ALU. Make a drawing in which only the specific subcomponents that create the 8-bit shift network are shown. Include the necessary interconnections. Include only the relevant part of fsel to control the network. The actual components used in Figure 1 and your 8-bit ALU drawing to construct the 8-bit shift network are not used in the drawing requested. They are stripped-down and flattened to contain only the specific components that do the shifting work. Hint: Each bit of the data path reduces to a simple and easily recognizable component described in EEL3701 and chapter 6 of the text. 7. Consider the 8-bit register. Compare the code that you produced with that shown in Figure 7.40 for a resettable flip-flop. 8. Show the VHDL code needed to make the load control on the register asynchronous (load happens whenever the load_enable is true regardless of the value of the clock).