High-level Synthesis of Embedded Hardware

advertisement

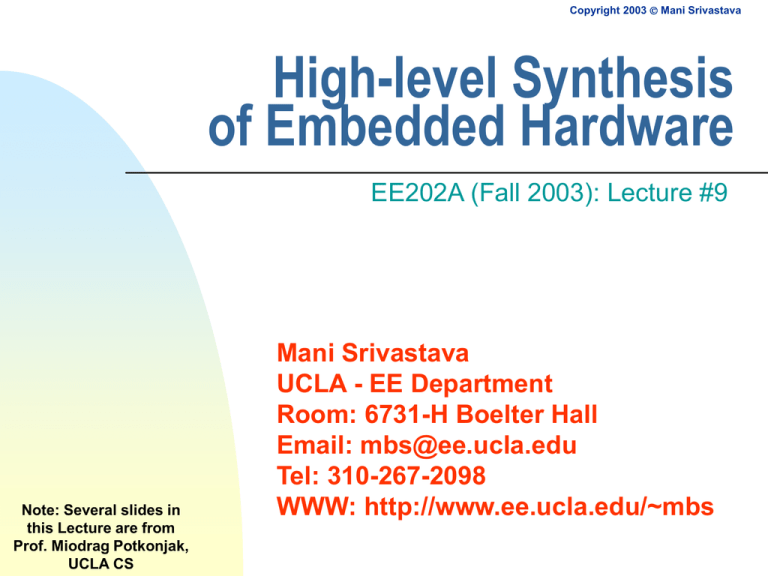

Copyright 2003 Mani Srivastava High-level Synthesis of Embedded Hardware EE202A (Fall 2003): Lecture #9 Note: Several slides in this Lecture are from Prof. Miodrag Potkonjak, UCLA CS Mani Srivastava UCLA - EE Department Room: 6731-H Boelter Hall Email: mbs@ee.ucla.edu Tel: 310-267-2098 WWW: http://www.ee.ucla.edu/~mbs Copyright 2003 Mani Srivastava 2 Overview High Level Synthesis Allocation, Assignment and Scheduling Estimations Transformations Copyright 2003 Mani Srivastava 3 Synthesis Process IN k + + + + + c 1 c2 + + c 4 Am pl (db ) c5 + D D -40 .0 c3 c6 d -60 .0 IN k + D -80 .0 +c D 200.0 4 00.0 Freq 600. 0 OUT + GP signal processor ASIC c5 + + c7 6 c8 + D + +c c1 c3 2 c4 -100 .0 interconnect D D -20 .0 -120 .0 0.0 ARCHITECTURE ALGORITHM APPLICATION D MCM memory LOGIC AND PHYSICAL SYNTHESIS HIGH-LEVEL SYNTHESIS S1 S2 S3 S4 6 Copyright 2003 Mani Srivastava Typical High-Level Synthesis System Copyright 2003 Mani Srivastava 7 High Level Synthesis Resource Allocation - How Much? Scheduling - When? Assignment - Where? Module Selection Template Matching & Operation Chaining Clock Selection Partitioning Transformations Copyright 2003 Mani Srivastava 8 Allocation, Assignment, and Scheduling Allocation: How Much? 2 adders 1 shifter 24 registers D + D >> + >> + Assignment: Where? Shifter 1 + >> >> + >> - Schedule: When? - Time Slot 4 Techniques Well Understood and Mature Copyright 2003 Mani Srivastava 9 Scheduling and Assignment 4 control steps +3 3 +1 1 *2 4 +2 2 *1 3 *3 4 Schedule 1 Control Step + 1 +3 1 +1 2 +2 3 *2 2 *1 4 *3 3 Schedule 2 Control Step + +1 1 +3 2 +2 2 +1 *2 3 +3 3 +2 *3 4 * * *1 *2 *3 4 * *1 Copyright 2003 Mani Srivastava 10 High Level Synthesis C GRAPHICS func fir (In) : Out = begin Out = In@1 * a; end D * * Signal Flow Database D * * + + D * D * * + + 1 x x 2 x 3 x * + + Min Bounds: 2 adders 1 multiplier 16 registers TRANSFORMATIONS SCHEDULING Time Adder Mult * ESTIMATIONS TEMPLATE MATCHING D D 4 x x MAPPING * + r eg r eg + mu lt * D + * 11 Copyright 2003 Mani Srivastava Algorithm Description 12 Copyright 2003 Mani Srivastava Control Data Flow Graph (CDFG) Copyright 2003 Mani Srivastava 13 Precedence Graph 14 Copyright 2003 Mani Srivastava Sequence Graph: Start and End Nodes 15 Copyright 2003 Mani Srivastava Hierarchy in Sequence Graphs 16 Copyright 2003 Mani Srivastava Hierarchy in Sequence Graphs (contd.) 17 Copyright 2003 Mani Srivastava Hierarchy in Sequence Graphs (contd.) Copyright 2003 Mani Srivastava 18 Implementation Control/Data Flow Graph (CDFG) 2 3 2 ... 2 1 1 ... Implementation Reg Reg Multiplier 4 3 2 ... Reg 0 4 7 ... 4 7 9 ... Reg Adder Copyright 2003 Mani Srivastava 19 Timing Constraints Time measured in “cycles” or “control steps” problem? Max & min timing constraints Copyright 2003 Mani Srivastava 20 Constraint Graphs Copyright 2003 Mani Srivastava 21 Operations with Unknown Delays Unknown but bounded e.g. Conditionals loops Unknown and unbounded e.g. I/O operations synchronization Completion signal Called “anchor nodes” Need to schedule relative to these anchors Copyright 2003 Mani Srivastava 22 Scheduling Under Timing Constraints Feasible constraint graph Well-posed constraint graph Timing constraints satisfied when execution delays of all the anchors is zero Necessary for existence of schedule Timing constraints satisfied for all values of execution delays Implies feasibility Feasible constraint graph is well-posed or can be made well-posed iff no cycles with unbounded weight exist 23 Copyright 2003 Mani Srivastava Ill-posed (a, b) vs. Well-posed (c) Timing Constraints Copyright 2003 Mani Srivastava 24 Conclusions High Level Synthesis Connects Behavioral Description and Structural Description Scheduling, Estimations, Transformations High Level of Abstraction, High Impact on the Final Design