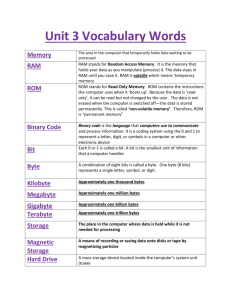

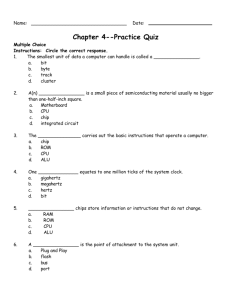

MEMORY DEVICES

advertisement

MEMORY DEVICES Week 13 BASICS OF SEMICONDUCTOR MEMORY Memory is the portion of a system for storing binary data in large quantities. Semiconductor memories consists of arrays of storage elements that are generally either latches or semiconductors UNITS: BITS : The smallest unit of binary data. BYTE : Unit of 8 bits or multiplies of 8 bit units . NIBBLES : A byte split into two 4 bit units WORD : Complete unit of information. 2 Semiconductor memory array ► Each storage element in a memory can retain either a 1 or 0 and is called a cell. Memories are made up of arrays of cells as shown in fig 1. .Each block in the memory array represents one storage cell ,and its location can be identified by specifying a row and a column. 3 Memory Address and Capacity ► ADDRESS: The location of a unit in a memory array .The address of a byte is specified only by row. The address of a bit is specified by row and column. CAPACITY: It is the total number of data units that can be stored. 4 Basic memory operations ► WRITE: The write operation puts data into a specified address in the memory ► READ: The read operation takes data out of a specified address in the memory ► ADDRESSING : The addressing operation which is part of both read and write ,selects the specified memory address. 5 System Bus ► DATA BUS: Data units go into memory during a write operation and come out of the memory during a read operation on a set of lines called the data bus. The data bus is bidirectional. 6 System Bus ► ADDRESS BUS: For a write or read operation , an address is selected by placing a binary code representing the desired address on a set of lines called address lines. ► The address code is decoded internally and the appropriate address is selected . The number of lines in the address bus depends on the addressing capacity.. 7 System Bus 8 bit FFFF FFFE Instruction 1 Instruction 2 Instruction 2 Word length 1 word instruction 2 word instruction Word: no. of bits micro-P recognizes and processes at a time ( 4 - 64bit ). ► Instruction: combination of bit patterns with specific meaning known to micro-P. ► Program: Set of all instructions. ► 64KByte 0001 0000 address 8 Illustration of the write operation. 9 ► To store a byte of data in memory ,a code held in the address register is placed on the address bus. Once the address code is on the bus ,the address decoder decodes the address and selects the specified location in the memory. ► The memory then gets a write command ,and the data byte held in the data register is placed on the data bus and stored in the selected memory address, thus completing the write operation. When a new byte is written into a memory address, the current data byte stored at that address is overwritten and destroyed. 10 ILLUSTRATION OF THE READ OPERATION 11 ILLUSTRATION OF THE READ OPERATION ► A code held in the address register is placed on the address bus. Once the address code is on the address bus ,the address decoder decodes the address and selects the specified location in the memory. ► The memory then gets a read command and a copy of the data byte that is stored in the selected memory address is placed on the data bus and loaded into the data register ,thus completing the read operation. When a byte is read form a memory address, it also remains stored at that address and is not destroyed .This is called non destructive read. 12 RAMs AND ROMs ► RAM(RANDOM ACCESS MEMORY) : A type of memory in which all addresses are accessible in an equal amount of time and can be selected in any order for a read or write operation .All RAM’S have both read and write capability. ► ROM(READ ONLY MEMORY): A type of memory where data can be stored permanently or semi permanently .Data can be read form a ROM ,but there is no write operation as in RAM. The ROM is a random access memory 13 THE RAM FAMILY ► The two categories of RAM are static RAM (SRAM) and dynamic RAM(DRAM) . ► SRAMs use flip flops as storage elements and can therefore store data indefinitely as long as dc power is applied ► DRAMs use capacitors as storage elements and can retain data very long without the capacitors being recharged by a process called refreshing . ► Both SRAMs and DRAMs are volatile memories because they will lose stored data when dc power is removed. 14 Figure 12--6 The RAM family. 15 SRAM Static RAM is a type of RAM that holds its data without external refresh, for as long as power is supplied to the circuit. 16 SRAM ORGANIZATION ► An asynchronous SRAM is one in which th e operation is not synchronized with a system clock .The logic symbol for a 32k x 8 bit memory is shown in fig. ► In the READ mode, the eight data bits that are stored in a selected address appear on the data output lines. In the write mode ,the eight data bits that are applied to the data input lines are stored at a selected address. The data input and data output lines (I/O1 through I/O8 ) are the same lines. During READ ,they act as output lines (I1 THROUGH I8) ► And during WRITE they act as input lines (O1 THROUGH O8) 17 18 The basic organization of 32kx 8 bit SRAM 19 SRAM ORGANIZATION ► The memory cell array is arranged in 256 rows and 128 columns ,each with 8 bits .There are actually 215 = 32,768 addresses and each address contains 8 bits. 20 DRAM Dynamic RAM is a type of RAM that only holds its data if it is continuously accessed by special logic called a refresh circuit. The difference between SRAM and DRAMs is the type of memory cell. DRAM memory cell consists of one transistor and a capacitor and is much simpler than SRAM cell . This allows much great densities in DRAM’S and results in greater bit capacities for a given chip area ,although much slower access time. 21 SRAM v DRAM ► Both volatile Power needed to preserve data ► Dynamic cell Simpler to build, smaller More dense Less expensive Needs refresh Larger memory units ► Static Faster Cache 22 ► Cache Memory: It is a relatively small ,high speed memory that stores the most recently used instructions or data from the large but slower main memory. It uses DRAM . 23 Cache ► Small amount of fast memory ► Sits between normal main memory and CPU ► May be located on CPU chip or module 24 THE ROM FAMILY 25 ROM Usage ► Permanent storage ► Microprogramming ► Library subroutines ► Systems programs (BIOS) ► Function tables ► No need to load from secondary device 26 ROM Organization ► The logic symbol for 256 x 4 ROM is shown below. 27 ► ► When any one of 256 binary codes is applied to the address lines ,four data bits appear on the outputs is the chip enable inputs are low The memory cell array is actually a 32 x 32 matrix as shown below. 28 29 ► A0 through A8 are decoded by the row decoder to select one of the 32 rows. ► Three of the 8 address lines A5 through A7 are decoded by the column decoder to select four of the 32 columns. When an 8 bit address code is applied ,a 4 bit data word appears on the data outputs when the chip enable lines are low. ► 30 ► The data stored in ROM are always there, whether the power is on or not. A ROM can be removed from the PC, and then replaced, and the data it contains will still be there. ► Data stored in these chips is unchangeable, provides a measure of security against accidental or malicious changes to its contents. Unlike RAM, which can be changed as easily as it is read We will look at five of them to see how they differ in the way they are programmed, erased, and reprogrammed 31 Mask ROM ► The mask ROM is usually referred to simply as a ROM. ► A regular ROM is constructed from hard-wired logic, encoded in the silicon itself to perform a specific function that cannot be changed. ► They consume very little power and reliable but cannot reprogram or rewrite. ► Several types of user programmable ROMs have been developed to overcome this disadvantage. 32 Programmable ROM (PROM) ► A mask ROM chip is very expensive and time-consuming to create in small quantities from scratch. ► Mainly, developers created a type of ROM known as programmable read-only memory (PROM). ► This is basically a blank ROM chip that can be written only once using special equipment called a PROM programmer. ► PROM chips have a grid of columns and rows just as ordinary ROMs do. 33 Programmable ROM (PROM) ► The difference is that every intersection of a column and row in a PROM chip has a fuse connecting them. ► Since all the cells have a fuse, the initial (blank) state of a PROM chip is all 1s. ► The user cans selectively burn/blow any of these fuse links to produce the desired stored memory data. ► A charge sent through a column will pass through the fuse in a cell to a grounded row indicating a value of 1. 34 Programmable ROM (PROM) ► To change the value of a cell to 0, you use a PROM programmer to send a specific amount of current to the cell to break the connection between the column and row by burning out the fuse. ► This process is known as burning the PROM. ► Very few bipolar PROMs are still available today. ► TMS27PC256 is a very popular CMOS PROM with a capacity of 32K 8. 35 Erasable Programmable ROM (EPROM) ► An EPROM is a ROM that can be erased and reprogrammed as often as desired. Once programmed. ► The EPROM is a non-volatile memory that will hold its stored data indefinitely. ► A little glass window is provided in the top of the ROM package. ► Ultraviolet light of a specific frequency can be shined through this window for a specified period of time, which will erase all cells at the same time so that an erased EPROM stores all 1s and allow it to be reprogrammed again. 36 Erasable Programmable ROM (EPROM) ► EPROMs are configured using an EPROM programmer that provides voltage at specified levels depending on the type of EPROM used. ► Obviously this is much more useful than a regular PROM, but it does require the erasing light. ► EPROMs are available in a wide range of capacities and access times. The 27C64 is an example of 8K x 8 CMOS EPROM 37 Electrically Erasable Programmable ROM (EEPROM) ► They require dedicated equipment and a laborintensive process to remove and reinstall them each time a change is necessary. ► The next type of ROM is the EEPROM, which can be erased under software control. ► This is the most flexible type of ROM, and is now commonly used for holding BIOS programs 38 Electrically Erasable Programmable ROM (EEPROM) ► In EEPROMs the chip does not have to be removed to be rewritten, the entire chip need not be fully erased to change a specific portion of it, and changing the contents does not require additional dedicated equipment. ► Instead of using UV light, you can return the electrons in the cells of an EEPROM to normal with the localized application of an electric field to each cell. 39 Electrically Erasable Programmable ROM (EEPROM) ► This erases the targeted cells of the EEPROM, which can then be rewritten. ► EEPROMs are changed 1 byte at a time, which makes them versatile but slow. ► The Intel 2864 is an example of EEPROM with 8K 8 array with 13 address inputs and eight data I/O pins 40 Flash Memory ► Flash memories are so called because of their rapid erase and write times. ► EEPROM chips speed is too slow to use in many products that required quick changes to the data stored on the chip. ► So a new type of EEPROM called Flash memory that uses in-circuit wiring to erase by applying an electrical field to the entire chip or to predetermined sections of the chip called blocks. 41 Flash Memory ► Flash memory works much faster than traditional EEPROMs because it writes data in chunks, usually 512 bytes in size, instead of 1 byte at a time. ► The 28F256A CMOS IC is an example of flash memory chip, which has a capacity of 32K 8. 42