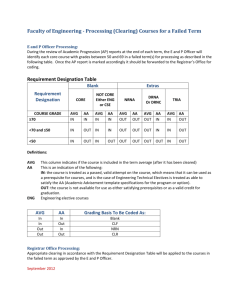

Using PowerPoint to Typeset Nice Presentations

advertisement

Universidad de Oviedo Lección 4 Teoría básica de los convertidores CC/CC (I) (convertidores con un único transistor) Diseño de Sistemas Electrónicos de Potencia 4º Curso. Grado en Ingeniería en Tecnologías y Servicios de Telecomunicación SEA_uniovi_CC1_001 Outline (I) Introducing switching regulators Basis of their analysis in steady state Detailed study of the basic DC/DC converters in continuous conduction mode Buck, Boost and Common and Buck-Boost converters different properties Introduction to the synchronous rectification Four-order converters SEA_uniovi_CC1_012 Outline (II) Study of the basic DC/DC converters in discontinuous conduction mode DC/DC converters with galvanic isolation How and The where to place a transformer in a DC/DC converter Forward and Flyback converters SEA_uniovi_CC1_023 Linear DC/DC conversion (analog circuitry) RV ig iO RL vg vE Av Feedback loop First idea = (vOiO)/(vgig) vO iO ig Vref Q ig vO/vg iO RL vg vE Av Feedback loop vO Vref Actual implementation Only a few components Robust No EMI generation Only lower output voltage Efficiency depends on input/output voltages Low efficiency Bulky SEA_uniovi_CC1_034 Linear versus switching DC/DC conversion Q ig iO RL vg vE Av Feedback loop ig vO vg iO RL vg PWM Vref vE vO Av Feedback loop Linear vO S Vref Switching (provisional) Features: vO_avg 100% efficiency Undesirable output voltage waveform t SEA_uniovi_CC1_045 Introducing the switching DC/DC conversion (I) S ig iO RL vg PWM vE vg t The AC component must be removed!! - Av Vref S RL C filter Vg vO vg iO Filter VO RL vO C filter PWM t It doesn’t work!!! S ig iO vg vO_avg vO Feedback loop ig vO vE Av Feedback loop Vref Basic switching DC/DC converter (provisional) SEA_uniovi_CC1_056 Introducing the switching DC/DC conversion (II) S ig iO Filter vg PWM RL ig iL vg iD + vD D - C iO L C RL vO Infinite voltage across L when S1 is opened It doesn’t work either!!! Including a diode S vg LC filter Vref Feedback loop iO L LC filter - Av vE ig vO iL S RL + vO - Vg vD VO t LC filter Basic switching DC/DC converter SEA_uniovi_CC1_067 Introducing the switching DC/DC conversion (III) iL S ig iD vg + vD D - iO L C RL + vO - iL iS ig S vg LC filter iD + L vD D - iO C RL + vO - Buck converter Starting the analysis of the Buck converter in steady state: L & C designed for negligible output voltage ripple (we are designing a DC/DC converter) iL never reaches zero (Continuous Conduction Mode, CCM) The study of the Discontinuous Conduction Mode (DCM) will done later iL DCM CCM iL t t SEA_uniovi_CC1_078 First analysis of the Buck converter in CCM (In steady-state) Analysis based on the specific topology of the Buck converter iL iS ig S vg vg iD + L vD D - iL iO C RL + + vO - L iO C vD RL + vO - LC filter vD vg vO vD vD_avg = vO t t dT T d: “duty cycle” vO = vD_avg = d·vg The AC component is removed by the filter This procedure is only valid for converter with explicit LC filter SEA_uniovi_CC1_089 Introducing another analysis method (I) Could we use the aforementioned analysis in the case of this converter (SEPIC)? ig L1 C1 + iS Vg S iD D iL2 L2 + C2 - R VO Obviously, there is not an explicit LC filter Therefore, we must use another method 10 SEA_uniovi_CC1_09 Introducing another analysis method (II) Powerful tools to analyze DC/DC converters in steady-state Step 1- To obtain the main waveforms (with no quantity values) using Faraday’s law and Kirchhoff’s current and voltage laws Step 2- To take into account the average value of the voltage across inductors and of the current through capacitors in steady-state Step 2 (bis)- To use the volt·second balance Step 3- To apply Kirchhoff’s current and voltage laws in average values Step 4- Input-output power balance 11 SEA_uniovi_CC1_10 Introducing another analysis method (III) Any electrical circuit that operates in steady-state satisfies: The average voltage across an inductor is zero. Else, the net current through the inductor always increases and, therefore, steady-state is not achieved The average current through a capacitor is zero. Else, the net voltage across the capacitor always increases and, therefore, steady-state is not achieved Vg L Circuit in steady-state + vL_avg = 0 C iC_avg = 0 12 SEA_uniovi_CC1_11 Introducing another analysis method (IV) Particular case of many DC/DC converters in steady-state: Voltage across the inductors are rectangular waveforms Current through the capacitors are triangular waveforms Vg L Circuit in steady-state + vL + Same areas v1 t - - dT C vL_avg = 0 vL iC -v2 Volt·second balance: V1dT – V2(1-d)T = 0 T iC_avg = 0 + iC - t Same areas 13 SEA_uniovi_CC1_12 Introducing another analysis method (V) Any electrical circuit of small dimensions (compared with the wavelength associated to the frequency variations) satisfies: Kirchhoff’s current law (KCL) is not only satisfied for instantaneous current values, but also for average current values Kirchhoff’s voltage law (KVL) is not only satisfied for instantaneous voltage values, but also for average voltage values KVL applied to Loop1 yields: Example iL1 Node1 L1 + vL1 - Vg S iS vg - vL1 - vC1 - vL2 = 0 vg - vL1_avg - vC1_avg - vL2_avg = 0 iC1 Therefore: vC1_avg = vg C1 + vC1 KCL applied to Node1 yields: + vL2 Loop1 - iL1 - iC1 - iS = 0 L2 iL1_avg - iC1_avg - iS_avg = 0 Therefore: iS_avg = iL1_avg 14 SEA_uniovi_CC1_13 Introducing another analysis method (VI) A switching converter is (ideally) a lossless system ig Input power: iO vg Switching-mode DC/DC converter RL Therefore: vgig_avg = vO2/RL Pg = vgig_avg + vO - Output power: PO = vOiO = vO2/RL Power balance: Pg = PO A switching-mode DC/DC converter as an ideal DC transformer ig_avg iO RL vg + vO - being N = vO/vg ig_avg = iOvO/vg = N·iO 1:N DC Transformer Important concept!! 15 SEA_uniovi_CC1_14 Steady-state analysis of the Buck converter in CCM (I) Step 1: Main waveforms. Remember that the output voltage remains constant during a switching cycle if the converter has been properly designed ig + vS iS - vg S iO iL iD + vD D - L Driving signal C RL L C RL vg t iL iO iL S on, D off + vO - + vO - t iS t During dT iO iL S off, D on L C RL iD + vO - t dT T During (1-d)T 16 SEA_uniovi_CC1_15 Steady-state analysis of the Buck converter in CCM (II) Step 1: Main waveforms (cont’) + vS vg iL S + vL L + vD D - C RL t + vO - iL L iO C RL vg + vO - vg-vO t - vO T iL + vL L t vL dT S off, D on, (1-d)T DiL iL_avg i L + vL - S on, D off, dT Driving signal iO iO C RL + vO - From Faraday’s law: DiL = vO(1-d)T/L 17 SEA_uniovi_CC1_16 Steady-state analysis of the Buck converter in CCM (III) Step 2 and 2 (bis): Average inductor voltage and capacitor current Average value of iC: ig + vL - iL iS iC_avg = 0 iD Volt·second balance over L: vg L Node1 S D iO iC C RL + vO - (vg - vO)dT - vO(1-d)T = 0 Therefore: vO = d·vg (always vO < vg) Driving signal Step 3: Average KCL and KVL: t KCL applied to Node1 yields: iL iL - iC - iO = 0 iL_avg iL_avg - iC_avg - iO = 0 Therefore: iL_avg = iO = vO/RL Step 4: Power balance: ig_avg = iS_avg = iOvO/vg = d·iO vg-vO t vL + - dT t - vO T 18 SEA_uniovi_CC1_17 Steady-state analysis of the Buck converter in CCM (IV) ig + vg vS iS S iD + vD D - Summary iO iL L C RL Driving signal + vO - vO = d·vg (always vO < vg) vSmax = vDmax = vg t vg vD t iL iO iL_avg = iO = vo/RL ig_avg = iS_avg = d·iO t iS DiL t iD_avg = iL_avg - iS_avg = (1-d)·iO DiL = vO(1-d)T/L iL_peak = iL_avg + DiL/2 = iO + vO(1-d)T/(2L) iS_peak = iD_peak = iL_peak iD t dT T 19 SEA_uniovi_CC1_18 Steady-state analysis of the Boost converter in CCM (I) Can we obtain vO > vg? Boost converter Step 1: Main waveforms ig + vL - i L L vg Driving signal iD iO D iS + - RL C S t + vO - iL t iS iL + vL - S on, D off, during dT DiL t L iD vg t i L + vL - S off, D on, during (1-d)T L dT iO C RL + vO - T From Faraday’s law: DiL = vgdT/L 20 SEA_uniovi_CC1_19 Steady-state analysis of the Boost converter in CCM (II) Step 2 and 2 (bis): Average values ig Average value of iC: + vL - i L L iC_avg = 0 Volt·second balance over L: iD vg iC D iS Node1 C S iO + - RL + vO - vgdT - (vO - vg)(1-d)T = 0 Therefore: vO = vg/(1-d) (always vO > vg) Driving signal Step 3: Average KCL and KVL: t KCL applied to Node1 yields: iD iD - iC - iO = 0 t iD_avg - iC_avg - iO = 0 Therefore: iD_avg = iL_avg(1-d) = iO = vO/RL Step 4: Power balance: ig_avg = iL_avg = iOvO/vg = iO/(1-d) DiL iD_avg vg vL t dT -(vO-vg) T 21 SEA_uniovi_CC1_20 Steady-state analysis of the Boost converter in CCM (III) ig + v L - i L - vD + L vg iS S D iD + vS - Summary iO iC C RL Driving signal + vO - vO = vg/(1-d) (always vO > vg) t vO vD t iL vSmax = vDmax = vO iL_avg = ig_avg = iO/(1-d) = vo/[RL(1-d)] t iS DiL t iS_avg = d·iL_avg = d·vo/[RL(1-d)] iD_avg = iO DiL = vgdT/L iL_peak = iL_avg + DiL/2 = iL_avg + vgdT/(2L) iS_peak = iD_peak = iL_peak iD iO t dT T 22 SEA_uniovi_CC1_21 Steady-state analysis of the Buck-Boost converter in CCM (I) Can we obtain either vO < vg or vO > vg? Buck-Boost converter ig iD iS iL S vg L + vL - iO D Driving signal vO + C + RL t iL DiL ig S on, D off, during dT t iL vg L iS + vL t - iD Charging stage t iO S off, D on, during (1-d)T + C vL + L - iL RL vO + Discharging stage dT T From Faraday’s law: DiL = vgdT/L 23 SEA_uniovi_CC1_22 Steady-state analysis of the Buck-Boost converter in CCM (II) Step 2 and 2 (bis): Average values Average value of iC: ig vgdT - vO(1-d)T = 0 iS iL iC_avg = 0 Volt·second balance over L: Node1 iD iO + vL - S vg L D iC C + RL vO + Therefore: vO = vgd/(1-d) Driving signal Step 3: Average KCL and KVL: t KCL applied to Node1 yields: iD iD - iC - iO = 0 iD_avg - iC_avg - iO = 0 Therefore: iD_avg = iL_avg(1-d) = iO = vO/RL Step 4: Power balance: ig_avg = iS_avg = iOvO/vg = iOd/(1-d) DiL iD_avg t vg vL t -vO dT T 24 SEA_uniovi_CC1_23 Steady-state analysis of the Buck-Boost converter in CCM (III) ig i + vS - S iL S vg L i D + vD - + vL - D - C Summary iO + RL Driving signal vO + vO = vgd/(1-d) (both vO < vg and vO > vg) t vO + vg vD t iL vSmax = vDmax = vO + vg iD_avg = iO DiL = vgdT/L t iS DiL t iL_avg = iD_avg/(1-d) = iO/(1-d) = vo/[RL(1-d)] iS_avg = ig_avg = d·iL_avg = d·vo/[RL(1-d)] iL_peak = iL_avg + DiL/2 = iL_avg + vgdT/(2L) iS_peak = iD_peak = iL_peak iD iO t dT T 25 SEA_uniovi_CC1_24 Common issues in basic DC/DC converters (I) L S vg + C D RL - + vO - Complementary switches + inductor Buck L S D vg + C S - RL d + vO - vg D 1-d L C + - RL + vO - Boost D S vg L Buck-Boost C + RL + vO - Voltage source The inductor is an energy buffer to connect two voltage sources 26 SEA_uniovi_CC1_25 Common issues in basic DC/DC converters (II) Diode turn-off vg L vg S D Buck L vg D S vO Boost + C RL - C + - RL + vO - + vO - The diode reverse recovery time is of primary concern evaluating switching losses Schottky diodes are desired from this point of view vO + vg S vg The diode turns off when the transistor turns on L D C Buck- + RL Boost + vO - In the range of line voltages, SiC diodes are very appreciated 27 SEA_uniovi_CC1_26 Comparing basic DC/DC converters (I) Generalized study as DC transformer (I) ig iO L S vg C - D L S iO iO RL + + vO - - RL C + vO - 1:N DC Transformer Buck: N= d (only vO < vg) Boost ig ig_avg vg D vg iO D - S vg RL Buck ig + vO - + L C + RL Boost: N= 1/(1-d) (only vO > vg) + vO - Buck-Boost: N= -d/(1-d) (both vO < vg and vO > vg) Buck-Boost 28 SEA_uniovi_CC1_27 Comparing basic DC/DC converters (II) Generalized study as DC transformer (II) ig_avg iO RL vg + vO - 1:N DC Transformer ig_avg = iON = iOd/(1-d) Buck: ig_avg = iON = iOd Boost: ig_avg = iON = iO/(1-d) Buck-Boost: ig_avg = iON = - iOd/(1-d) 29 SEA_uniovi_CC1_28 Comparing basic DC/DC converters (III) Electrical stress on components (I) iS ig vg + vS iO - S iD + vD D - RL + vO - DC/DC converter Buck: Boost: Buck-Boost: vSmax = vDmax = vg vSmax = vDmax = vO vSmax = vDmax = vO + vg iS_avg = ig_avg iL_avg = ig_avg iS_avg = ig_avg iL_avg = iO iD_avg = iO iD_avg = iO iD_avg = iL_avg - iS_avg iS_avg = iL_avg - iD_avg iL_avg = iS_avg + iD_avg 30 SEA_uniovi_CC1_29 Comparing basic DC/DC converters (IV) Example of electrical stress on components (I) 1 A (avg) 2A L S 100 V C D + + - RL 50 V - 100 W Buck, 100% efficiency 2A 1 A (avg) D S 100 V L C - + RL + 50 V 100 W Buck-Boost, 100% efficiency vS_max = vD_max = 100 V iS_avg = iD_avg = 1 A iL_avg = 2 A FOMVA_S = FOMVA_D = 100 VA vS_max = vD_max = 150 V iS_avg = 1 A iD_avg = 2 A iL_avg = 3 A FOMVA_S = 150 VA FOMVA_D = 300 VA Higher electrical stress in the case of BuckBoost converter Therefore, lower actual efficiency 31 SEA_uniovi_CC1_30 Comparing basic DC/DC converters (V) Example of electrical stress on components (II) 4 A (avg) 2A L 25 V D S C vS_max = vD_max = 50 V iS_avg = iD_avg = 2 A iL_avg = 4 A FOMVA_S = FOMVA_D = 100 VA + + - RL - 50 V 100 W Boost, 100% efficiency 2A 4 A (avg) D S 25 V L C - + RL + 50 V 100 W Buck-Boost, 100% efficiency Higher electrical stress in the case of BuckBoost converter Therefore, lower actual efficiency vS_max = vD_max = 75 V iS_avg = 4 A iD_avg = 2 A iL_avg = 6 A FOMVA_S = 300 VA FOMVA_D = 150 VA 32 SEA_uniovi_CC1_31 Comparing basic DC/DC converters (VI) Price to pay for simultaneous step-down and stepup capability: Higher electrical stress on components and, therefore, lower actual efficiency Converters with limited either step-down or step-up capability: Lower electrical stress on components and, therefore, higher actual efficiency 33 SEA_uniovi_CC1_32 Comparing basic DC/DC converters (VII) Example of power conversion between similar voltage levels based on a Boost converter 6.12 A (avg) 50 V 5A L 1.12 A (avg) D S C + - RL 300 W Boost, 98% efficiency + - 60 V vS_max = vD_max = 60 V iS_avg = 1.12 A iD_avg = 5 A iL_avg = 6.12 A FOMVA_S = 67.2 VA FOMVA_D = 300 VA Very high efficiency can be achieved!!! 34 SEA_uniovi_CC1_33 Comparing basic DC/DC converters (VIII) The opposite case: Example of power conversion between very different and variable voltage levels based on a BuckBoost converter 20 - 2 A (avg) 5A D S 20 - 200 V L C - + RL + 60 V 300 W Buck-Boost, 75% efficiency Remember previous example: FOMVA_S = 67.2 VA FOMVA_D = 300 VA vS_max = vD_max = 260 V iS_avg_max = 20 A iD_avg_max = 5 A iL_avg = 25 A FOMVA_S_max = 5200 VA FOMVA_D = 1300 VA High efficiency cannot be achieved!!! 35 SEA_uniovi_CC1_34 Comparing basic DC/DC converters (IX) One disadvantage exhibited by the Boost converter: The input current has a “direct path” from the input voltage source to the load. No switch is placed in this path. As a consequence, two problems arise: Large peak input current in start-up No over current or short-circuit protection can be easily implemented (additional switch needed) L vg S D + C Boost - RL + vO - Buck and Buck-Boost do not exhibit these problems 36 SEA_uniovi_CC1_35 Synchronous rectification (I) To use controlled transistors (MOSFETs) instead of diodes to achieve high efficiency in low output-voltage applications This is due to the fact that the voltage drop across the device can be lower if a transistor is used instead a diode The conduction takes place from source terminal to drain terminal In practice, the diode (Schottky) is not removed L S idevice MOSFET D Diode L S1 S2 L S1 S2 vdevice 37 SEA_uniovi_CC1_36 Synchronous rectification (II) In converters without a transformer, the control circuitry must provide proper driving signals In converters with a transformer, the driving signals can be obtained from the transformer (self-driving synchronous rectification) Nowadays, very common technique with low output-voltage Buck converters L L S2 S1 vO S2 S1 D C - RL + vO - Synchronous Buck Q’ PWM Q vg + Av Vref Feedback loop 38 SEA_uniovi_CC1_37 Input current and current injected into the output RC cell (I) If a DC/DC converter were an ideal DC transformer, the input and output currents should also be DC currents As a consequence, no pulsating current is desired in the input and output ports and even in the current injected into the RC output cell ig iS vg + vS S iRC iD + vD D - DC/DC converter Desired current ig C + + v - RL - O Desired current iRC t t 39 SEA_uniovi_CC1_38 Input current and current injected into the output RC cell (II) iRC ig ig S vg t L + C D Noisy - iRC ig L D vg t t Low noise Buck ig S Low noise + - RL C + vO - iRC t Noisy Boost ig iRC D ig S t Noisy RL + vO - iRC vg L Buck-Boost C + RL + vO - iRC t Noisy 40 SEA_uniovi_CC1_39 Input current and current injected into the output RC cell (III) Adding EMI filters iRC ig LF CF vg + - L S D + C - + vO - RL Buck Filter iRC ig L D vg S CF Boost vg CF Filter + - C Filter ig LF LF + - D S L Buck-Boost + LF CF + - RL + vO - R + L vO + iRC C Filter 41 SEA_uniovi_CC1_40 Four-order converters (converters with integrated filters) L1 ig iD C1 + iS vg Same vO/vg as Buck-Boost Same stress as Buck-Boost vC1 = vg Filtered input D - vC1 iL2 L2 S + C2 - vO RL ig SEPIC Same vO/vg as Buck-Boost Same stress as Buck-Boost vC1 = vg + vO Filtered input and output iS C1 vg iS vg - + L1 + C2 iL1 iD Zeta - vC1 S iD D - RL vO C2 + Cuk L2 D L2 iL2 C1 + iL2 vC1 S L1 - RL vO Same vO/vg as Buck-Boost Same stress as Buck-Boost vC1 = vO Filtered output 42 SEA_uniovi_CC1_41 DC/DC converters operating in DCM (I) Only one inductor in basic DC/DC converters The current passing through the inductor decreases when the load current decreases (load resistance increases) iL L ig vg S D DC/DC converter iL iL_avg iO RL t + vO - Driving signal t dT T Buck: Boost: Buck-Boost: iL_avg = iO iL_avg = iO/(1-d) iL_avg = iS_avg + iD_avg = diO/(1-d) + iO = iO/(1-d) 43 SEA_uniovi_CC1_42 DC/DC converters operating in DCM (II) When the load decreases, the converter goes toward Discontinuous Conduction Mode (DCM) Decreasing load iL RL_1 iL_avg t iL Operation in CCM RL_2 > RL_1 iL_avg t iL RL_crit > RL_2 iL_avg t Boundary between CCM and DCM It corresponds to RL = R L_crit 44 SEA_uniovi_CC1_43 DC/DC converters operating in DCM (III) Decreasing load What happens when the load decreases below the critical value? iL iL DCM RL_crit iL_avg If a synchronous rectifier (SR) is used, iL_avg the operation depends on the driving signal RL_3 > RL_crit t RL_3 > RL_crit iL_avg DCM w. diode rectifier t CCM w. SR iL starts if a diode is used as CCM operation is possible with synchronous rectifier with a proper driving signal (synchronous rectifier with signal almost complementary to the main transistor) t 45 SEA_uniovi_CC1_44 DC/DC converters operating in DCM (IV) Remember: iL_avg = iO (Buck) or iL_avg = iO/(1-d) (Boost and Buck-Boost) iL For a given duty cycle, lower average RL > RL_crit CCM w. SR iL_avg t For a given duty cycle, higher average RL > RL_crit iL value (due to the negative area) lower output current for a given load lower output voltage DCM w. diode iL_avg t value (no negative area) higher output current for a given load higher output voltage The voltage conversion ratio vO/vg is always higher in DCM than in CCM (for a given load and duty cycle) 46 SEA_uniovi_CC1_45 DC/DC converters operating in DCM (V) How can we get DCM (of course, with a diode as rectifier) ? iL After decreasing the inductor inductance t iL iL After decreasing the switching frequency t After decreasing the load (increasing the load resistance) t 47 SEA_uniovi_CC1_46 DC/DC converters operating in DCM (VI) Three sub-circuits instead of two: The transistor is on. During d·T The diode is on. During d’·T Both the transistor and the diode are off. During (1- Driving signal t iL iL_avg t iD vg d-d’)T Example: Buck-Boost converter ig iD_avg S + vg - -vO d’·T t iD iL t vL d·T iS L ig vg D C + RL vO + iO iL T + vL - iO L + vL - During d·T + C vL + RL L - iL During d’·T vO + iL + vL L - During (1-d-d’)T 48 SEA_uniovi_CC1_47 DC/DC converters operating in DCM (VII) Voltage conversion ratio vO/vg for the Buck-Boost converter in DCM ig iL Driving signal iL vg iL_max t iL_avg iD vg t iL_max iD_avg + d·T - -vO d’·T T vL From Faraday’s law: vg = LiL_max/(dT) - During d·T + C vL + RL L - iL iO vO + And also: vO = LiL_max/(d’T) During d’·T t vL L + t Also: iD_avg = iL_maxd’/2, iD_avg = vO/R And finally calling M = vO/vg we obtain: M =d/(k)1/2 where k =2L/(RT) 49 SEA_uniovi_CC1_48 DC/DC converters operating in DCM (VIII) The Buck-Boost converter just on the boundary between DCM and CCM iL RL = RL_crit iL_avg t Due to being in DCM: M = vO/vg = d/(k)1/2, where: k = 2L/(RT) Due to being in CCM: N = vO/vg = d/(1-d) Just on the boundary: M = N, R = Rcrit, k = kcrit Therefore: kcrit = (1-d)2 The converter operates in CCM if: k > kcrit The converter operates in DCM if: k < kcrit 50 SEA_uniovi_CC1_49 DC/DC converters operating in DCM (IX) Summary for the basic DC/DC converter Buck Boost N=d 1 N= 1-d Buck-Boost N= 2 M= 1+ 4k 1+ 2 d kcrit = (1-d) kcrit_max = 1 1+ M= 4d2 1+ k 2 kcrit = d(1-d)2 kcrit_max = 4/27 M= d 1-d d k kcrit = (1-d)2 kcrit_max = 1 k = 2L/(RT) 51 SEA_uniovi_CC1_50 DC/DC converters operating in DCM (X) CCM versus DCM Driving signal Driving signal t t vD t iL iS iD T - Lower conduction losses in CCM (lower rms values) iL_avg - Lower losses in DCM when S turns on and D turns off t - Lower losses in CCM when S turns off t t dT vD - Lower inductance values in DCM (size?) t iL iL_avg iS t iD t t dT T 52 SEA_uniovi_CC1_51 Achieving galvanic isolation in DC/DC converters (I) - A two-winding magnetic device is needed - The volt·second balance in the case of magnetic devices with two windings must be used From Faraday’s law: + v1 - + v2 n1:n2 vg Circuit in steadystate vi = ni d/dt B D= B - A = (vi/ni)·dt A In steady-state: (D)in a period = 0 And therefore: (vi /ni)avg = 0 Volt·second balance: If all the voltages are DC voltages, then: CCM: dT(V1/n1) – (1-d)T(V2/n2) = 0 DCM: dT(V1/n1) –d’T(V2/n2) = 0 53 SEA_uniovi_CC1_52 Achieving galvanic isolation in DC/DC converters (II) Transformer models Model 1 Lm1 n1:n2 Ll1 Model 2 Ll2 Lm1 n1:n2 n1:n2 Model 1: Model 2: Model 3: Circuit Theory element Magnetic transformer with perfect coupling Magnetic transformer with real coupling At least the magnetizing inductance must be taken into account analyzing DC/DC converters 54 SEA_uniovi_CC1_53 Achieving galvanic isolation in DC/DC converters (III) Where must we place the transformer? Lm1 n1:n2 In a place where the average voltage is zero ig iO + vg vS S - + vD D - RL + vO - DC/DC converter 55 SEA_uniovi_CC1_54 Achieving a Buck converter with galvanic isolation (I) L S vg C Buck D + - RL No place with average voltage equal to zero + vO - New node with possible zero average voltage L vg S D S on S off C + vO - + - RL D2 L vg S Lm1 D1 + C - RL + vO - n1:n2 It does not work!! 56 SEA_uniovi_CC1_55 Achieving a Buck converter with galvanic isolation (II) vextra A circuit to apply a given DC voltage across Lm1 when S is off S off S on D2 n3 L vg D1 Lm1 + C - RL + vO - n1:n2 n1:n1:n2 D2 L Lm1 vg S D1 + C - RL + vO - D3 Final implementation: the Standard design: vextra = vg n3 = n1 Forward converter 57 SEA_uniovi_CC1_56 The Forward converter As the Buck converter replacing vg with vgn2/n1 n1:n1:n2 L D1 Lm1 + C L + vO - S & D2 on, D1 & D3 off, during dT S & D2 off, D1 on, S RL - D3 vg iO iL D2 C RL vgn2/n1 + vO - Inductor magnetizing stage im1 + D3 on, during d’T im1 during (1-d)T iO iL L C RL vg + vO - Inductor demagnetizing stage Lm1 vL - Transformer reset stage - Transformer magnetizing stage + vg Lm1 vL vO = dvgn2/n1 vSmax = 2 vg dmax = 0.5 (reset transformer) 58 SEA_uniovi_CC1_57 Achieving a Buck-Boost converter with galvanic isolation (I) D S vg L BuckBoost S vg C + RL vO + There is a place with average voltage equal to zero: the inductor D Inductor and transformer integrated into only one - magnetic device (two-winding inductor) vO + C Lm1 L + RL RL vO + n1:n2 S on vg S off S D C L + n1:n2 59 SEA_uniovi_CC1_58 Achieving a Buck-Boost converter with galvanic isolation (II) vg D S C L + RL vO + n1:n2 Two-winding inductor D n1:n2 L1 L2 + C - RL + vO - S on, D off, during dT ig + vg L1 vL - Charging stage iO vg + S Final implementation: the Flyback converter S off, D on, during (1-d)T vLn2/n1 - C L2 + RL vO + Discharging stage 60 SEA_uniovi_CC1_59 The Flyback converter Analysis in steady-state in CCM Volt·second balance: L1 vg S dTvg/n1 - (1-d)TvO/n2 = 0 D n1:n2 L2 + C - RL + vO - vO = vg(n2/n1)·d/(1-d) Therefore, the result is the same as Buck-Boost converter replacing vg with vgn2/n1 vSmax = vg + vOn1/n2 vDmax = vgn2/n1 + vO Very simple topology Useful for low-power, low-cost converters Critical “false transformer” (two-winding inductor) design 61 SEA_uniovi_CC1_60 Achieving other converters with galvanic isolation (I) L1 L D C Boost S vg RL + - + + vO - vg S It is not possible with only one transistor!! L1 C1 + n1:n2 - L2 C2 + - Vg D S Cuk C3 C1 L2 n1:n2 D + C2 - RL vO SEPIC Zeta converter is also possible RL VO + vO = vg(n2/n1)d/(1-d) vSmax = vg + vOn1/n2 vDmax = vgn2/n1 + vO Like the Flyback converter 62 SEA_uniovi_CC1_61