Sequential logic implementation

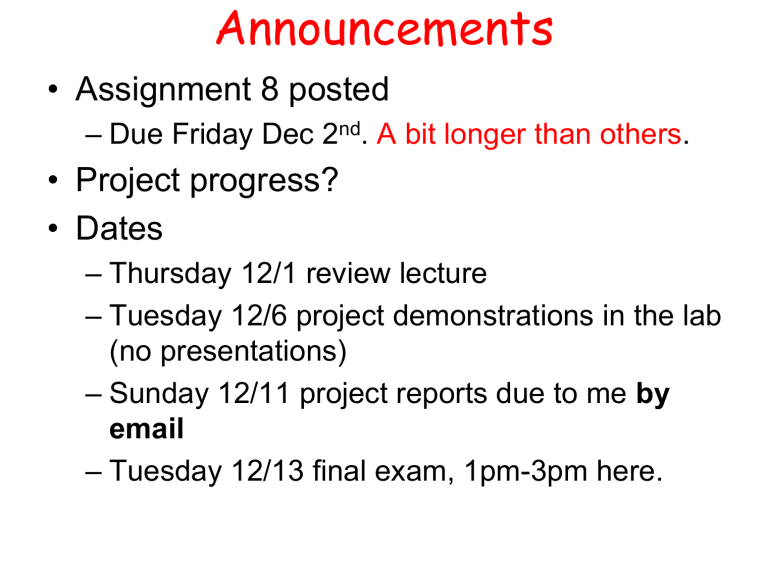

Announcements

• Assignment 8 posted

– Due Friday Dec 2 nd .

A bit longer than others

.

• Project progress?

• Dates

– Thursday 12/1 review lecture

– Tuesday 12/6 project demonstrations in the lab

(no presentations)

– Sunday 12/11 project reports due to me

by email

– Tuesday 12/13 final exam, 1pm-3pm here.

Last Topic!

• Analog / Digital Conversion

Introduction

• Most signals are naturally analog (e.g. a voltage)

• Digital techniques are often more useful: data storage, processing, computing, error free signal transmission etc.

• We need ways to convert analog signals to digital

• Want A/D converters to be fast, accurate and cheap

• There are various methods of analog to digital conversion

• Digital to analog conversion is also important: e.g. CRT video monitors convert computer generated digital information into analog signals used to guide an electron beam. MP3 players convert music stored digitally into analog signals to drive an amplifier and speaker.

• Digital to analog conversion is an integral part of some types of analog to digital converters

Digital to Analog Conversion

• D/A or DAC: convert a quantity specified as a binary number to a voltage or current proportional to the value of the digital input

• Simplest approach - recall the weighted summing opamp circuit:

MSB ( ‘ eights’ –smallest R)

V out

R f

R

0 b

0

R f

R

1 b

1

R f

R

2 b

2

R f

R

3 b

3

V out

2

10 b

0

2 b

1

5

2

2 .

5 b

2

2

1 .

25 b

3

V out

1

5

b

0

2 b

1

4 b

2

8 b

3

Binary weighting - if each binary input is a 5V signal, Voltage output corresponds to 1V per bit.

LSB ( ‘ ones ’ – largest R)

N-bit Weighted DAC

• What if we want higher resolution (more bits)?:

V out

V out

R / 2

2 n

1

R

V ref

V ref

2 n

a

0

a

0

2 a

1

2 a

1

4 a

2

...

2 n

1 a n

1

4 a

2

...

2 n

1 a n

1

• In practice, binary weighted adder is not used for resolution exceeding 4 bits

• Typical value of smallest R=10kΩ,

• Consider a 10-bit converter, V ref

• Three problems:

=1V, giving 1/1024~1mV resolution

• Biggest R = 2 9 R =5M Ω; too large (noisy, expensive, large error)!

• Precision: for LSB to be meaningful, R must be precise to 1 part in 2 10

• R=10.00

± 0.01k

Ω - 0.1%

• Conversion time:

• If C stray

=100pF, RC=5M Ω

100pF=0.5ms (too slow)

Solution: R-2R Ladder

V out

V out

R f

R

V ref

D

0

16

D

1

8

D

2

4

D

3

2

• Using just R and 2R removes the problems of the weighted adder

• R values are reasonable

• Precision requirements can be met

• RC time constants are small

These are digital switches

R-2R Ladder: Thevenin analysis

V out

R f

R

V ref

D

0

16

D

1

8

D

2

4

D

3

2

How do we end up with these weights? Apply Thevenin's...

D/A converter Specifications

• In reality, you can buy DACs prebuilt in a chip. Some specs to look out for:

• Resolution (precision): maximum output resolution is 1 bit in 2 n -1 times the voltage range (Size of the smallest possible voltage step)

• Accuracy: percentage error in voltage output

• Linearity: deviation of the stepwise output from a straight line

• Settling time: Minimum time required for conversion

• Output range: Range of output analog voltage for max digital input swing

• Input digital code: e.g. straight binary, BCD, Gray code

Ideal DAC:

V out digital input

D/A converter Specifications

R-2R ladder

What is the best resolution attainable for a range of 10V?

What is the maximum allowable conversion frequency given a settling time of 1 μs?

D/A converter Specifications

What is the best resolution attainable for a range of 10V?

=10/(2 8 -1) = 39.2mV

What is the maximum allowable conversion frequency given a settling time of 1 μs?

D/A converter Specifications

What is the best resolution attainable for a range of 10V?

=10/(2 8 -1) = 39.2mV

What is the maximum allowable conversion frequency given a settling time of 1 μs?

=1/ 1 μs = 1MHz

input voltage comparator

ADC Type I: Digital Ramp ADC

storage register

• Counter counts up with each clock pulse

• DAC outputs a slightly higher voltage each clock pulse

• Compare this to the input voltage using the comparator

• Comparator output goes to counter and parallel input/output shift register

• when the DAC output exceeds the input voltage

• comparator output goes low

• Storage register receives a clock pulse and latches the counter values

• Counter receives a LOAD input to reset to 0

ADC Type I: Digital Ramp ADC

Big drawback: sampling interval depends on voltage level:

Sampling is also slow - need to count up from 0 every time.

ADC Type II: Tracking ADC

• A more efficient method

• Compares analog signal input with the output of a DAC connected to an up/down counter.

• Comparator determines whether DAC output is larger or smaller than analog input

• If DAC output is smaller, comparator output starts counter counting up

• If DAC output is larger, comparator starts counter counting down

• The digital output "tracks" the analog input signal by changing 1 bit at a time

• The rate at which the counter changes is determined by an external clock

Digital output has to "catch up" to analog input

ADC Type II: Tracking ADC

• Digital output is not latched so is never perfectly stable

• oscillates by +/- 1 bit. "bit bobble"

ADC Type III: Successive Approximation ADC

successive approximation register

Shift register

Uses a digital feedback loop which iterates once per clock cycle

• Similar structure to the digital slope ADC, but replace the counter with a "successive approximation register" (SAR)

• The SAR is used to make a digital estimate of the analog input based on the comparator output

• The estimate is converted back to analog by the DAC and compared to the input

• The cycle repeats until the "best estimate is achieved

• Best estimate is then latched into the output shift register

• Different algorithms exist for the SAR the most common is the binary search algorithm

Binary search example

• The algorithm can be summarized as "go to the midpoint of the non-excluded range"

• Assume an 8-bit ADC with an analog input voltage range of 0 to 10V

• 0V = 00000000

2

= 0

10

• 10V = 11111111

2

=255

10

• one bit (Least Significant Bit, LSB) is 10/255=39.22mV

• Assume a signal input of 7.09V

• The comparator outputs

• HIGH if the estimate < the signal input

• LOW if the estimate > the signal input

• The SAR does the following (n is the current clock cycle):

• comparator is HIGH (estimate too small): adds 1 to MSB-(n+1)

• comparator is LOW (estimate too large): subtracts 1 from MSB-(n+1)

start at the midpoint adds 1 to MSB-(n+1)=bit 7 subtracts 1 from MSB-(n+1)=bit 6

• This algorithm is guaranteed to find the best possible estimate in a number of clock cycles equal to the number of bits

• In this example, best estimate was on the 7 th clock cycle, but the difference between the 7 th and 8 th is within the ADC resolution

• The binary search algorithm is fast and efficient

• It completes its estimation in a fixed number of clock cycles

• The final result is latched after a fixed number of clock cycles (=number of bits), so the sampling occurs at regular intervals (unlike the digital ramp ADC)

Example ADC question:

• A 10-bit digital slope integrating A/D converter has a full-scale input of 10V.

If the clock period is 15 μS, how long will it take to convert an input of 4V?

How long for an input of 10V?

10 bits means 2 10 =1024 levels.

Full scale input of 10V means each level is 10V/1024=9.77mV

4V corresponds to 4/9.77

10 -3 =409.6 - round up to 410

A clock period of 15 μs mean 4V will take 15μs

410 =6.15ms

10V will take 15 μs

1024=15.36ms

Example ADC question:

• A 10-bit digital slope integrating A/D converter has a full-scale input of 10V.

If the clock period is 15 μS, how long will it take to convert an input of 4V?

How long for an input of 10V?

10V will take 15 μs

1024=15.36ms

• What increase in speed can be gained by using a 12-bit successive approximation converter instead of the digital slope converter, assuming a full-scale input voltage.?

• A 12-bit SA converter will take 12 clock cycles = 180 μs, regardless of the input voltage

• so for 10V full scale input, the speed increase is 15.36ms/180 μs

=85.3 times.

• So the SA converter is both faster and more accurate (12 bits gives

4096 levels, compared to 1024 levels for 10 bit)