01intro

advertisement

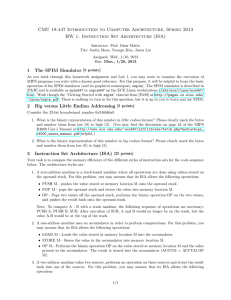

CSIE30300 Computer Architecture Unit 01: Introduction Hsin-Chou Chi [Adapted from material by Patterson@UCB and Irwin@PSU] Where is the Market? Millions of Computers 1200 1122 1000 892 Embedded Desktop Servers 862 800 600 488 400 290 200 0 93 3 1998 114 3 1999 135 4 2000 129 4 2001 131 5 2002 Instruction Set Architecture (ISA) ISA: An abstract interface between the hardware and the lowest level software of a machine that encompasses all the information necessary to write a machine language program that will run correctly, including instructions, registers, memory access, I/O, and so on. Enables implementations of varying cost and performance to run identical software ISA Type Sales Other SPARC Hitachi SH PowerPC Motorola 68K MIPS IA-32 ARM 1400 Millions of Processor 1200 1000 800 600 400 200 0 1998 1999 2000 2001 2002 Moore’s Law In 1965, Gordon Moore predicted that the number of transistors that can be integrated on a die would double every 18 to 24 months (i.e., grow exponentially with time). Amazingly visionary – million transistor/chip barrier was crossed in the 1980’s. 2300 transistors, 1 MHz clock (Intel 4004) - 1971 16 Million transistors (Ultra Sparc III) 42 Million transistors, 2 GHz clock (Intel Xeon) – 2001 55 Million transistors, 3 GHz, 130nm technology, 250mm2 die (Intel Pentium 4) - 2004 140 Million transistor (HP PA-8500) Processor Performance Increase Performance (SPEC Int) 10000 Intel Pentium 4/3000 DEC Alpha 21264A/667 DEC Alpha 21264/600 Intel Xeon/2000 1000 DEC Alpha 4/266 100 DEC AXP/500 DEC Alpha 5/500 DEC Alpha 5/300 IBM POWER 100 HP 9000/750 10 IBM RS6000 SUN-4/260 MIPS M2000 MIPS M/120 1 1987 1989 1991 1993 1995 Year 1997 1999 2001 2003 DRAM Capacity Growth 512M 256M 128M 1000000 64M Kbit capacity 100000 16M 10000 4M 1M 1000 256K 64K 100 16K 10 1976 1978 1980 1982 1984 1986 1988 1990 1992 1994 1996 1998 2000 2002 Year of introduction Impacts of Advancing Technology Processor logic capacity: performance: increases about 30% per year 2x every 1.5 years ClockCycle = 1/ClockRate 500 MHz ClockRate = 2 nsec ClockCycle 1 GHz ClockRate = 1 nsec ClockCycle 4 GHz ClockRate = 250 psec ClockCycle Memory DRAM capacity: 2x every 1.5 years, now 2x every 2 years memory speed: 1.5x every 10 years cost per bit: decreases about 25% per year Disk capacity: increases about 60% per year Example Machine Organization Workstation design target 25% of cost on processor 25% of cost on memory (minimum memory size) Rest on I/O devices, power supplies, box Computer CPU Memory Devices Control Input Datapath Output PC Motherboard Closeup Inside the Pentium 4 Processor Chip MIPS R3000 Instruction Set Architecture Registers Instruction Categories Load/Store Computational Jump and Branch Floating Point - R0 - R31 coprocessor PC HI Memory Management Special LO 3 Instruction Formats: all 32 bits wide OP rs rt OP rs rt OP rd sa immediate jump target Q: How many already familiar with MIPS ISA? funct